DisEnchantment

Golden Member

Speculate at will

Last edited:

RGT is at it again these days, with the usual +30% IPC speculation of course but also no frequency regression this time, he even risk 6GHz as being possible...im still waiting for the low ballers to explain how from zen 1 to 4, core width didn't grow and OOOE window increased a small amount ( especially relative to others ) while doing ~ 50% more ipc and yet going to 6 wide plus a whole new fronted we know nothing about except its big shinny and new and we are getting -5 to 15% with clock regression.....

its not like there arent cores that size with that much more IPC on the market.

How do we know if there has been any delay, when no official release date has ever been communicated?Although he seemed to get the details about the Zen 5 delay right

pffft... this is not an Intel thread... 😛

That was on A0 silicon which had a clock regression 😛I’ve had more than 1 person tell me that CB R23 1T is >=2800 which is a >=40% increase. If I had to take a geomean of Zen 5 leakers it’d probably be a 40% 1T perf increase overall.

I don’t personally believe that but it’s at least consistent. The only person saying it’s not hype™ is MLID who’s track record is spotty. Although he seemed to get the details about the Zen 5 delay and 800 series chipset right .. so ymmv.

Yes. In the A17/M3, the decider got upped from 8 to 9 wide.A17P is 9-wide according to this.

Now, that's the good stuff

Cardyak’s Microarchitecture Cheat Sheet

docs.google.com

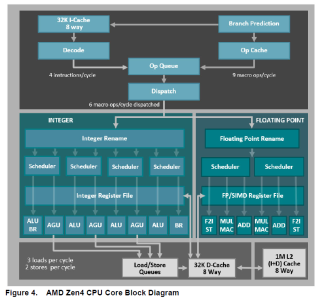

Intel's P-cores have been 6-wide since GLC.Zen 4 4-wide

RPC 5-wide

RWC 6-wide (re-compiled software could theoretically run faster than Raptor Lake Refresh)

Source for above 3 is ChatGPT (please correct if it spitted out misinformation)

M3 width probably no one knows. M1 is supposed to be 8-wide according to this: https://news.ycombinator.com/item?id=25394447

X4 10-wide (yowza!)

Zen 5 possibly 8-wide

Wow. Looks like ARM is shooting for the moon.

SuperWide UltraEfficientWow. Looks like ARM is shooting for the moon.

Yeah, from numbers alone you'd think GLC+ onward cores belong to a different weight class.Zen has been 4 wide/6 dispatch all the way from Zen 1 to Zen 4?

That is crazy.

Ever noticed theCan we do a microarchitecture comparison of Zen 4, Raptor Cove(or RWC), M3 P-core and Cortex X4?

POST THREAD button at the top right of each subforum page?Thanks.There’s a great uarch cheat sheet for all of you nerds:

Cardyak’s Microarchitecture Cheat Sheet

docs.google.com

A17P is 9-wide according to this.

Good luck entering such a thread without wearing a hazmat suit.Ever noticed thePOST THREADbutton at the top right of each subforum page?

Zen1-Zen4 4-way x86 decoderZen 4 4-wide

RPC 5-wide

RWC 6-wide (re-compiled software could theoretically run faster than Raptor Lake Refresh)

Source for above 3 is ChatGPT (please correct if it spitted out misinformation)

M3 width probably no one knows. M1 is supposed to be 8-wide according to this: https://news.ycombinator.com/item?id=25394447

X4 10-wide (yowza!)

Zen 5 possibly 8-wide

Wow. Looks like ARM is shooting for the moon.

What does 1+3 / 1+5 mean?Zen1-Zen4 4-way x86 decoder

Conroe(Core 2) - SunnyCove/CypressCove 4-way x86 dekoder(1+3)

GoldenCove - RedwoodCove 6-way x86 dekoder(6(1+5(?)))

Complex vs simple decoder. Intel traditionally has one complex with the rest simple.What does 1+3 / 1+5 mean?

Also why specify it's an x86 decoder? We know it's an x86 core.

Ooh. Is Intel the only one doing this?Complex vs simple decoder. Intel traditionally has one complex with the rest simple.

Ooh. Is Intel the only one doing this?

So all x86 CPUs should have at least one complex decoder. ARM doesn't need one.RISC has far fewer instructions than CISC, and each basic instruction is executed in a single clock cycle. CISC's instructions can be complex and perform multiple tasks in a single instruction. CISC's complex instruction set makes x86 chips harder to design because the chip has to be able to account for the complex instructions, making x86 chips typically more expensive.

Because RISC uses simple instructions and tends to use less power per instruction, this makes ARM chips ideal for devices that need longer battery life.

Zen has been 4 wide/6 dispatch all the way from Zen 1 to Zen 4?

That is crazy.

Ooh. Is Intel the only one doing this?