- Mar 3, 2017

- 1,779

- 6,798

- 136

It's some laptop dGPU, Rembrandt iGPU should max out below 3k.7735hs is zen 3... at 70w it's 8000 vs 9000 only?

...if the 9950X is configured to ≤90 W, yes. (Or let's say ≤110 W due to IOD and GMI overhead.)closer to 9950x score

Could you link the source?Strix halo looking good

Here we go again, could you show R23 scaling with memory bandwidth?looks disappointing if true but scores should be much higher, it's x16 zen5 + double bandwidth

And have you measured how well 9950x scores in the 13inch tablet with tons of Asus bloatware installed and pre-release firmware limited to 80W?R23 is only ~33000, should be higher closer to 9950x score

It's cinememeif true but scores should be much higher, it's x16 zen5 + double bandwidth

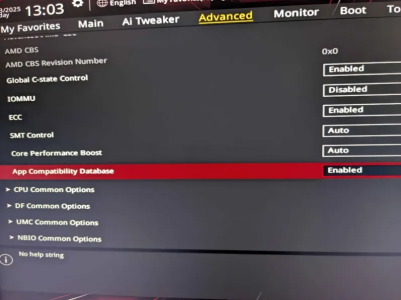

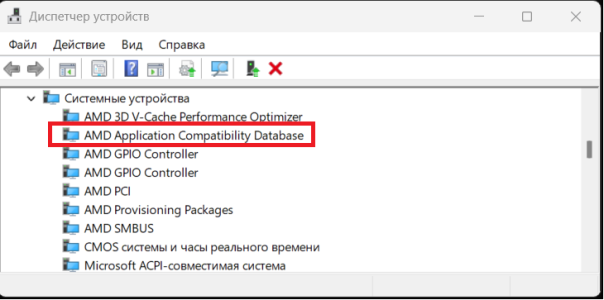

hey guys agesa 1203 bios solve unknown device problem

just need install new chipset driver

AMD chipset driver 7.01.08.129

*Improves performance for 2CCD Raphael and Granite Ridge CPUs

It's 7600S IIRC.It's some laptop dGPU, Rembrandt iGPU should max out below 3k.

Slightly worried, are they possibly bringing the 9950X scheduling to 7950X?Wonder what programs is supported and how it affects performance..

New chipset driver is recommened for the newest ageasa

And have you measured how well 9950x scores in the 13inch tablet with tons of Asus bloatware installed and pre-release firmware limited to 80W?

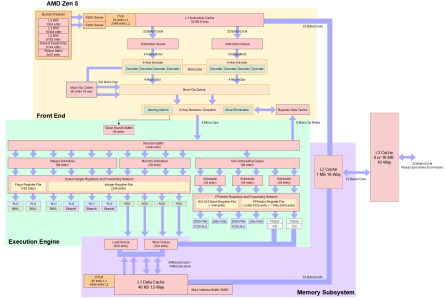

So unless the interconnect clocks massively higher, the read throughput from IOD to CCD remains the same as on GNR.No power, same high bandwidth, 32 bytes per cycle in both directions, lower latency.

2/3 benefits already met, the last can be saved for Medusa, plus they can juice the clocks for the given platform.

So unless the interconnect clocks massively higher, the read throughput from IOD to CCD remains the same as on GNR.

Ahhh they cucked it to 1*32B fabric-side. Lame.So unless the interconnect clocks massively higher, the read throughput from IOD to CCD remains the same as on GNR.

That's what it always did.oh they're clocking the IF in-between 1-2 GHz.

I haven't finished watching the interview at the time I posted this and was hoping that they'd at least clock it higher with STXH, but no.Ahhh they cucked it to 1*32B fabric-side. Lame.

That's what it always did.

So as always after AMD interview a guessing game begins. What is the actual CCD to IOD connection speed.

So unless the interconnect clocks massively higher, the read throughput from IOD to CCD remains the same as on GNR.

UPD: oh they're clocking the IF in-between 1-2 GHz.

It might be a transcript issue, he might have misspoken, or it might be another case of "two decoders are able to work on 1T instruction stream" caseSo the first big change between a Granite or a 9950X3D and this the Strix Halo always the die to die interconnect. Low power, same high bandwidth, 32 bytes per cycle in both directions, lower latency.

We are able to get power benefits. Because prior to that, we had a GMI PHY that lived in there and that consumed a whole lot of power in order to be able to send this over high frequencies over short distances. Here we are clocking it at a way less than the 20 gigs that the GMI was being clocked at.

Up to 32G actually. But you never see any GMI data really, it's all abstracted by the SMU.Also I was surprised that GMI physical is clocked at 20GHz and I am not sure how it works exactly if the clocks reported by software show 2GHz.

Classic AMD - the cheapo company.So unless the interconnect clocks massively higher, the read throughput from IOD to CCD remains the same as on GNR.

UPD: oh they're clocking the IF in-between 1-2 GHz.

But that's how they keep innovating. By staying cheap. Look at Intel. Threw mounds of cash at their problems and almost at the verge of bankruptcy.Classic AMD - the cheapo company.

Why would you use a GPU with this part outside of eventual upgrades (when games become too demanding to run, which won’t happen for a long time)2 x USB4 + other gen 3 and 2.

16 PCIe lanes.

You can have an x8 to an external GPU + 2xSSD, or 4x to an I/O hub, 8x to a GPU, and 1xssd, or 4xssd, or a few thunderbolt ports and a couple SSDs.

Meh, bandwidth is fine.Except they will pair it with crappy LPDDR5. Mendocino has 5500 MT/s and it's almost atrocious.

My 7950x won’t do +50 even. It jumps off the motherboard and runs away if I even think about enabling PBO.How about +100 or +150?

Fallen, Intel has.And this at the end:

Overall, other aspects remain mostly unchanged but there is a high probability that AMD's Ryzen sales could overtake Intel this quarter. Budget Ryzen 9000 non-X CPUs will go neck and neck against Arrow Lake non-K, though AMD has a clear platform advantage.

Ignore early benchmarks, and ignore benchmarks from a single product. Consider it a ballpark.In the notes it says Asus TUF A16 Advantage Edition, so it could be a Radeon 7600S or a 7700S, difficult to judge because it seems not set at max TDP.

Sadly, best ASUS has given me is AGESA 1.2.0.2bAMD have gotten their own APO it seems

View attachment 114842

View attachment 114843

Wonder what programs is supported and how it affects performance..

New chipset driver is recommened for the newest ageasa

LameI haven't finished watching the interview at the time I posted this and was hoping that they'd at least clock it higher with STXH, but no.

So yeah, we're stuck with 64 GB/s read bw per CCD.

They have to save some gains for next gen. 🤣Classic AMD - the cheapo company.

I think you just have a crappy mobo with insufficient power stages and other inferior components. ITX mobos aren't supposed to be for overclocking.My 7950x won’t do +50 even. It jumps off the motherboard and runs away if I even think about enabling PBO.

Try using Mendocino. It's sad. The latency is over 100ns.Meh, bandwidth is fine.

Not a transcript issue, that's exactly what he said. 3:36It might be a transcript issue, he might have misspoken, or it might be another case of "two decoders are able to work on 1T instruction stream" case

Where Intel vacates, a far more capable and relentless competitor will arrive in NV with their ARM SoC for Windows this year. Intel had a sizable process leadership when they went around as chipzilla that masked architecture deficiencies, and x86 was unassailable in computing. All that is gone now.But that's how they keep innovating. By staying cheap. Look at Intel. Threw mounds of cash at their problems and almost at the verge of bankruptcy.

But with people now going crazy for the X3D, maybe they will start spending a bit more to give us better products.

Well, while I personally was looking forward to wider link to CCD in Halo, to be fair, there is an iGPU for whatever they need. It's not like on Granite Ridge, where 9950x has more flops than the integrated GPU iircClassic AMD - the cheapo company.

But do we have any source on Strix Point beyond C&C diagram. They sometimes make mistakes. I mean there is already precedent for Strix Halo CCD to have 32B read/write as Turin CCDs does that [and I would guess Granite Ridge CCDs as well would be capable if not for the old iOD, but this is only my guess, no data to back that up].I think he simply misspoke and meant that 32B/cycle behavior is similar to that of Strix Point.

Well, their only proposed candidate is still far way, will lack Windows support most likely, and is locked down to one mini-workstation SKU, so I guess AMD might enjoy some wins this year, and the assault from the ARM competition will come in 2026, once again pure guesswork, but they are people lurking on this forum that have some access to actual roadmaps so maybe they would be able to give more accurate info.NV AI+Gaming Halo range