- Mar 3, 2017

- 1,779

- 6,798

- 136

Most of them. January announcement most likely, but only a rumor.Any good reviews on the 9800X3D? Also any word of larger core count 3D chips?

Any good reviews on the 9800X3D? Also any word of larger core count 3D chips?

It does support DDR5-5600, it says so on the product page.Probably not a huge priority. Why would anyone want it in AM5, and get slightly crippled 4x Zen 5 cores (half AVX-512), quite crippled 8x Zen 5c, crippled L3, no V-Cache. And as far as I know, Strix Point only supports LPDDR5, not regular DDR5.

Slightly more interesting would be a Strix Point MiniPC or even more interesting, Strix Halo MiniPC.

Meh, scheduling issues can be worked around, provided you don’t mind rebooting.MSI 9950X3D show it will be worse in games than 9800X3D. Scheduling issues will undoubtedly cause anomalies that will bring its average vs 9800X3D down a bit.

It is a “must buy” for me when it launches and I have the funds, which should hopefully be soonish.Insane if true. 9950X is going to be an absolute unit of a CPU, especially with new RTX 5090 coming soon. Sad times for intel though, they are being relegated to bulldozer levels of performance.

That's the fastest (currently) qualified jedec speed for SO-DIMMs. As for the earlier comment, not everyone will need full implementation AVX-512. The one on Strix is no worse than Zen4, which was praised for it's performance as well. In addition, AMD has stated that the same AGESA changes that improved the cross CCX latencies for the desktop chips also help Strix.It does support DDR5-5600, it says so on the product page.

View attachment 111341

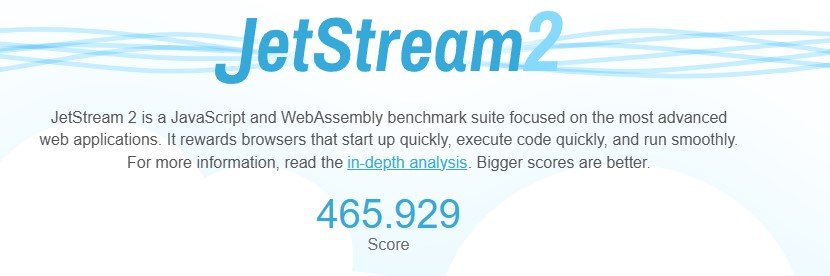

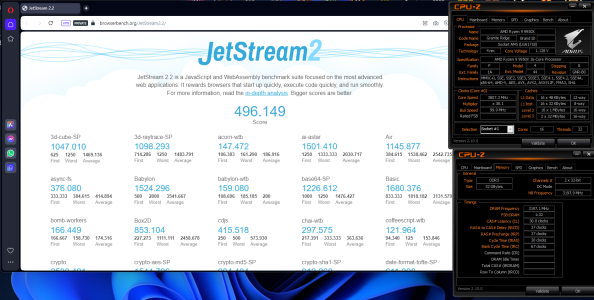

The browser you use to run this makes a huge difference. Firefox got a 300 something for me, Edge got below:Zen 5 has been dethroned in Jetstream 2 by M4 Max, so anybody with a well tuned 9950X/9700X want to beat this score?

This was quite a big jump, M3 Max scored 311 in this test, slower than a 7950X

View attachment 111317

Start skimming from here: https://forums.anandtech.com/thread...ranite-ridge-ryzen-9000.2607350/post-41331851Any good reviews on the 9800X3D? Also any word of larger core count 3D chips?

This is my 9950X (DDR5 6400) with OperaZen 5 has been dethroned in Jetstream 2 by M4 Max, so anybody with a well tuned 9950X/9700X want to beat this score?

This was quite a big jump, M3 Max scored 311 in this test, slower than a 7950X

View attachment 111317

As a matter of fact it is worse in some aspects due to "scheduler full" problems, but generally should do better thanks to other improvementsAs for the earlier comment, not everyone will need full implementation AVX-512. The one on Strix is no worse than Zen4, which was praised for it's performance as well

IIRC that leak showed the same 5.2ghz Fmax boost for the 9950x3d, which may hint that both CCDs are v-cached, or that the 2nd CCD is trash binMSI 9950X3D show it will be worse in games than 9800X3D. Scheduling issues will undoubtedly cause anomalies that will bring its average vs 9800X3D down a bit.

Could you run this benchmark with SMT off? Browser benchmarks typically see some gains with it turned off.

they nerf ryzen 5 hard lol. Probably 2+4 or 3+3, and only 4CU. Basically Small Phoenix replacementView attachment 111358

Kraken Point is 4+4 ?

run it, but no difference in this caseCould you run this benchmark with SMT off? Browser benchmarks typically see some gains with it turned off.

But with 256-bit memory bus maybe?View attachment 111387

Ryzen AI Max Pro 380 is overlapping with the Ryzen AI HX 370 in terms of specifications.

Same 16 CU RDNA3.5 GPU, but only 6 CPU cores?