- Mar 3, 2017

- 1,779

- 6,798

- 136

It is only supposed to denote the difference between various CPU designers approach to Heterogeneous cores.big.BIG is confusing. I know what you mean but suppose Zen 5 is heterogenous the big cores that were in Zen 4 will be little in Zen 5 and even bigger cores will come to Zen 5. It's either big.LITTLE or hybrid.

Well... This is interesting.You could even argue that such a part could be implemented even with Zen 4. 8 Core N5 Zen 4 CCD + 16 Core N4 Zen 4C CCD. And they are exact instruction compatible but different performance and efficiency characteristics. If RTL was putting lots of MT heat, I wouldn't be surprise to hear new 24 core parts from AMD once Bergamo is out.

From my understanding of the TSMC SoIC roadmap, there is no N7/N6 on N3. Just N5 on N3.

Same again for N7/N6 on N5. Its just N5 on N5.

N7/N6 on N5 is not on the TSMC SoIC roadmap.I am pretty sure Zen 4 V-Cache will be N6 V-Cache on top of N5 base die.

N7/N6 on N5 is not on the TSMC SoIC roadmap.

View attachment 69711

From https://semiwiki.com/semiconductor-...posium-review-advanced-packaging-development/

But maybe I'm reading that table wrong?

There was another image shared by TSMC in 2021 that came with the one you posted;

View attachment 69765

Its clear on the qualifications available and the time expected for each. At the time Andreas Schilling shared this image on twitter and was directly asked about N7/N6 on N5;

I guess that anyone's guess is as good as anyone's elses. MLID is saying N6 on N5... which to me is enough to say that mixed configs don't exist atm

Mixed configurations are definitely possible and are coming as far as I'm aware.There was another image shared by TSMC in 2021 that came with the one you posted;

View attachment 69765

Its clear on the qualifications available and the time expected for each. At the time Andreas Schilling shared this image on twitter and was directly asked about N7/N6 on N5;

I guess that anyone's guess is as good as anyone's elses. MLID is saying N6 on N5... which to me is enough to say that mixed configs don't exist atm

Fair enough. Perhaps I've read too much into the roadmaps - just find it odd that they wouldn't mention N6-N5 but they do mention N5-N3.Mixed configurations are definitely possible and are coming as far as I'm aware.

No comment on which product I'm referring to specifically

(Although realistically you could probably guess because if it's not RDNA3...)

Mixed configurations are definitely possible and are coming as far as I'm aware.

No comment on which product I'm referring to specifically

(Although realistically you could probably guess because if it's not RDNA3...)

Fair enough. Perhaps I've read too much into the roadmaps - just find it odd that they wouldn't mention N6-N5 but they do mention N5-N3.

Excitedly awaiting your comments...

So just a very quick observation. Given your die size assumptions, your desktop layout might be plausible, but server definitely not. Or at least not without a billion package layers. You need a lot more shoreline for DDR and PCIe, and can't really route those under the compute dies.I admit that I belong to the camp Replacement of IFOP interconnect.

This I had already checked in the Zen 4 thread and I also had dreamed of it being replaced already before Zen 3 launched.

Since then I have been asking myself how an EFB-based solution could look like from a Layout-perspective and if there will be a need to employ some rather crazy geometries. So I finally decided to generate some layouts based on the following assumptions:

I am basing my mockups on the measurements of this article https://wccftech.com/amd-epyc-genoa...-sp5-lga-6096-server-platform-details-leaked/ and this picture:

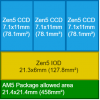

- AMD has to keep the AM5 socket and might want to keep the SP5 socket as well. So there are restrictions to the allowed area. For AM5 I assumed that a square of 21.4x21.4mm² should be realistic - by reordering some of the "bird food". For SP5 I am sticking to the area used by the 12 CCD Genoa SKU - which is well known through the Gigabyte Leaks.

- AMD will want to stick with using the same CCD(s) for Server as well as Client and maybe even Mobile in the future.

- AMD will want to minimize the amount of different dies - so a solution like SPR were 2 different dies are needed for 4 tiles might not be sufficient for them.

- There will be no daisy-chaining of CCDs. There will be no tunneling an EFB under a CCD to reach another CCD. So all CCDs will have to share a common border to the IOD.

- As a guideline I assumed that the IOD-area of Server and Client Zen 5 will be in the same ballpark as Zen 4. Of course this could be totally wrong. For example I would assume that EFB takes less area than an IFOP with the same bandwith, but who knows.

View attachment 69848

So if I assume only a moderate increase of the CCD the following layouts could be possible for the speculated 128c EPYC Turin and Client Zen 5 with up to three CCD.

Zen 5 Client

View attachment 69849

There is still some area left to increase the height of the CCD.

EPYC Turin 128c 16 CCD

View attachment 69850

- I decided for the IOD to be cut in half and reconnected by EFB as well. As the IOD is basically a cross-bar I do not know if EFB could provide enough bandwith at <7mm width.

- Also here there is about 0.5mm height-increase possible for the CCD increasing it to a bit over 80mm².

Of course this is all just armchair-engineering. But somehow it nicely fits.

Excitedly awaiting your comments...

Which kind of fan out would you guess? I mean EFB is also a fan out variation - IIRC based on TSMC InFo-L(SI). Do you mean InFo-R(DL)? If so: I have so far failed to really understand the concept. Is the RDL silicon-based? If not, what is the significant difference to the current IFOP?EFB is very costly, they're going to use Fan-out insted, most likely. If they even want to use it.

Please be aware that I did not use the total package area. I only used the area where dies are placed on already in this generation. So wouldn't the factors mentioned already apply to this generation?So just a very quick observation. Given your die size assumptions, your desktop layout might be plausible, but server definitely not. Or at least not without a billion package layers. You need a lot more shoreline for DDR and PCIe, and can't really route those under the compute dies.

I admit that I belong to the camp Replacement of IFOP interconnect.

We do see core counts growing, and we will continue to increase the number of cores in our core complex that are shared under an L3. As you point out, communicating through that has both latency problems, and coherency problems, but though that's what architecture is, and that's what we signed up for. It’s what we live for - solving those problems. So I'll just say that the team is already looking at what it takes to grow to a complex far beyond where we are today, and how to deliver that in the future.

BTW, they have done routing of IFOP signal lines from underneath the CCD. EPYC Milan has 14 layers in the substrate to handle all of this.There will be no tunneling an EFB under a CCD to reach another CCD. So all CCDs will have to share a common border to the IOD.

LSI has an active interconnect together with RDL. By active I mean repeaters, transceivers, routers, switch, mux/demux etc. which has transistors switching on and off.Which kind of fan out would you guess? I mean EFB is also a fan out variation - IIRC based on TSMC InFo-L(SI). Do you mean InFo-R(DL)? If so: I have so far failed to really understand the concept. Is the RDL silicon-based? If not, what is the significant difference to the current IFOP?

I admit that I belong to the camp Replacement of IFOP interconnect.

This I had already checked in the Zen 4 thread and I also had dreamed of it being replaced already before Zen 3 launched.

Since then I have been asking myself how an EFB-based solution could look like from a Layout-perspective and if there will be a need to employ some rather crazy geometries. So I finally decided to generate some layouts based on the following assumptions:

I am basing my mockups on the measurements of this article https://wccftech.com/amd-epyc-genoa...-sp5-lga-6096-server-platform-details-leaked/ and this picture:

- AMD has to keep the AM5 socket and might want to keep the SP5 socket as well. So there are restrictions to the allowed area. For AM5 I assumed that a square of 21.4x21.4mm² should be realistic - by reordering some of the "bird food". For SP5 I am sticking to the area used by the 12 CCD Genoa SKU - which is well known through the Gigabyte Leaks.

- AMD will want to stick with using the same CCD(s) for Server as well as Client and maybe even Mobile in the future.

- AMD will want to minimize the amount of different dies - so a solution like SPR were 2 different dies are needed for 4 tiles might not be sufficient for them.

- There will be no daisy-chaining of CCDs. There will be no tunneling an EFB under a CCD to reach another CCD. So all CCDs will have to share a common border to the IOD.

- As a guideline I assumed that the IOD-area of Server and Client Zen 5 will be in the same ballpark as Zen 4. Of course this could be totally wrong. For example I would assume that EFB takes less area than an IFOP with the same bandwith, but who knows.

View attachment 69848

So if I assume only a moderate increase of the CCD the following layouts could be possible for the speculated 128c EPYC Turin and Client Zen 5 with up to three CCD.

Zen 5 Client

View attachment 69849

There is still some area left to increase the height of the CCD.

EPYC Turin 128c 16 CCD

View attachment 69850

- I decided for the IOD to be cut in half and reconnected by EFB as well. As the IOD is basically a cross-bar I do not know if EFB could provide enough bandwith at <7mm width.

- Also here there is about 0.5mm height-increase possible for the CCD increasing it to a bit over 80mm².

Of course this is all just armchair-engineering. But somehow it nicely fits.

Excitedly awaiting your comments...

View attachment 69855

From LinkedIn somewhere in the past (now nuked)

Seems they are still planning SerDes PHY for 3nm nodes, but at least double the speed of Zen 4 GMI3 (32Gbps). GMI2 had 25 Gbps speed.

But the core layout would be different I suppose compared to Z4, they could 3D stack cores on L3 for instance in one CCD.

Meaning more cores in 1 CCD/CCX. Already Mike Clark alluded to this.

BTW, they have done routing of IFOP signal lines from underneath the CCD. EPYC Milan has 14 layers in the substrate to handle all of this.

View attachment 69856

LSI has an active interconnect together with RDL. By active I mean repeaters, transceivers, routers, switch, mux/demux etc. which has transistors switching on and off.

RDL is passive, just Cu interconnects similar to Metal Layers on the core, but obviously nowhere as dense. But far denser than routing in package substrate. You can fab RDL with old litho tech.

I think it should be something that AMD can manufacture in house without relying on TSMC for assembly. They have a massive new plant in Malaysia dedicated to advanced packaging which will come online in 1H23.

RDNA3 and MI300 could probably give some hints.

RDL is not a silicon-based thing. It's like an advanced substrate, placed on top of standard substrate, made for routing lines inbetween usual substrate and the die.Which kind of fan out would you guess? I mean EFB is also a fan out variation - IIRC based on TSMC InFo-L(SI). Do you mean InFo-R(DL)? If so: I have so far failed to really understand the concept. Is the RDL silicon-based? If not, what is the significant difference to the current IFOP?

Please be aware that I did not use the total package area. I only used the area where dies are placed on already in this generation. So wouldn't the factors mentioned already apply to this generation?

polymerinnovationblog.com

polymerinnovationblog.com

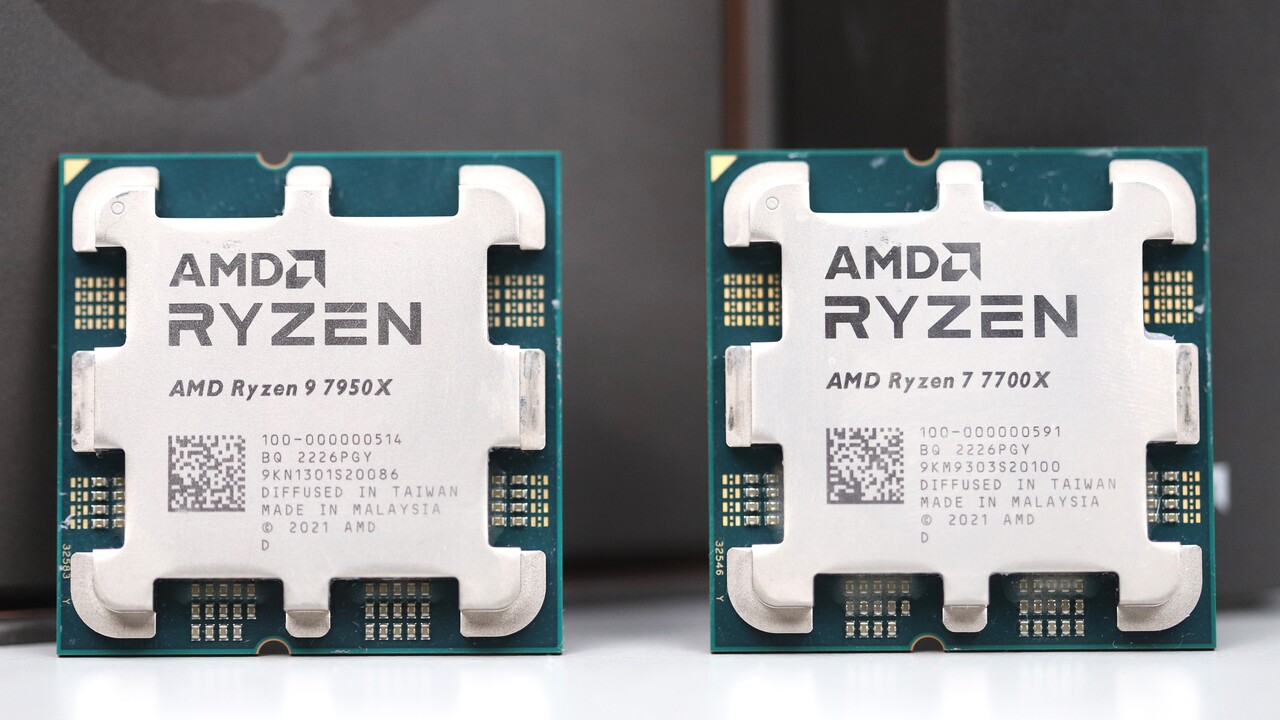

I'm going to copy @DisEnchantment's image above to use as reference.Please be aware that I did not use the total package area. I only used the area where dies are placed on already in this generation. So wouldn't the factors mentioned already apply to this generation?

AMD can just save costs by using 8P chip + 16E chip in the form of Zen5 + Zen4c. The down bins from Turin and Bergamo sold to consumers to save money. TSMC is no longer offering discounts to even their largest customers.I admit that I belong to the camp Replacement of IFOP interconnect.

This I had already checked in the Zen 4 thread and I also had dreamed of it being replaced already before Zen 3 launched.

Since then I have been asking myself how an EFB-based solution could look like from a Layout-perspective and if there will be a need to employ some rather crazy geometries. So I finally decided to generate some layouts based on the following assumptions:

I am basing my mockups on the measurements of this article https://wccftech.com/amd-epyc-genoa...-sp5-lga-6096-server-platform-details-leaked/ and this picture:

- AMD has to keep the AM5 socket and might want to keep the SP5 socket as well. So there are restrictions to the allowed area. For AM5 I assumed that a square of 21.4x21.4mm² should be realistic - by reordering some of the "bird food". For SP5 I am sticking to the area used by the 12 CCD Genoa SKU - which is well known through the Gigabyte Leaks.

- AMD will want to stick with using the same CCD(s) for Server as well as Client and maybe even Mobile in the future.

- AMD will want to minimize the amount of different dies - so a solution like SPR were 2 different dies are needed for 4 tiles might not be sufficient for them.

- There will be no daisy-chaining of CCDs. There will be no tunneling an EFB under a CCD to reach another CCD. So all CCDs will have to share a common border to the IOD.

- As a guideline I assumed that the IOD-area of Server and Client Zen 5 will be in the same ballpark as Zen 4. Of course this could be totally wrong. For example I would assume that EFB takes less area than an IFOP with the same bandwith, but who knows.

View attachment 69848

So if I assume only a moderate increase of the CCD the following layouts could be possible for the speculated 128c EPYC Turin and Client Zen 5 with up to three CCD.

Zen 5 Client

View attachment 69849

There is still some area left to increase the height of the CCD.

EPYC Turin 128c 16 CCD

View attachment 69850

- I decided for the IOD to be cut in half and reconnected by EFB as well. As the IOD is basically a cross-bar I do not know if EFB could provide enough bandwith at <7mm width.

- Also here there is about 0.5mm height-increase possible for the CCD increasing it to a bit over 80mm².

Of course this is all just armchair-engineering. But somehow it nicely fits.

Excitedly awaiting your comments...

Slight is Zen 1+ increase (just ~3%). Anything above 10% is not a small jump in IPC.

AMD can just save costs by using 8P chip + 16E chip in the form of Zen5 + Zen4c. The down bins from Turin and Bergamo sold to consumers to save money. TSMC is no longer offering discounts to even their largest customers.