- Mar 3, 2017

- 1,779

- 6,798

- 136

If STX3 is indeed being canceled, that would be pretty bad cause Intel is coming strong with Lunar Lake targeting ultraportables. So far, Lunar Lake is pretty much confirmed to have 4P+4E designs with Battlemage grahics engine that made by TSMC N3, the specs match with STX3. So I would hope AMD resume the designsAFAIK Strix Point (4+8, 16 CU, 4nm monolithic) is STX1, it was originally 8+4 and 3nm but got redefined due to TSMC issues. Strix Halo is (at least internally) called SAR(Sarlak) and STX3 has been cancelled entirely.

STX3 being canceled certainly seems like an odd choice. Leaves no direct successor to PHX2. It's extra weird because the equivalent in Intel's lineup (2+8 ADL, for example) seems to be their best selling chip.AFAIK Strix Point (4+8, 16 CU, 4nm monolithic) is STX1, it was originally 8+4 and 3nm but got redefined due to TSMC issues. Strix Halo is (at least internally) called SAR(Sarlak) and STX3 has been cancelled entirely.

Hmm, come to think of it, I have wild speculation about STX3..... We all know about Intel Lunar Lake design so would AMD, so it is possible that AMD has made redesign of STX3 by porting it to N3E to fit in more CPU and GPU cores with double memory bandwidth.STX3 being canceled certainly seems like an odd choice. Leaves no direct successor to PHX2. It's extra weird because the equivalent in Intel's lineup (2+8 ADL, for example) seems to be their best selling chip.

Doesn't make a lot of sense at this "early" point in time, not to mention the voltage sensitivity of having L3 as a V-cache die on top.

The recent burn out CPUs are prove of the current unsafe design/control.

I don't think L2 has grown significant as suggested for the simple reason that the die size has to be kept at the same size as before as much as possible despite node shrinks that mostly used to add other stuff (5-wide expansion) or squeeze the c/d variants. Not to mention SRAM doesn't shrink well.

The interesting rumor bit is that L2 is somehow unified. I can only guess it's somewhat similar to IBM's Z15 virtual cache or moving toward that kind of solution. I'm guessing it's more like keeping core-bound data at closer L2 cells while larger data at more distant & area sharing cells. It's still conjecture at this point. Hence, depending on how you view it the L2 has grown even if it's not.

TBH investing into many mobile designs is weird given the OEM adoption track record.

AMD keeps reiterating how the reuse and tape out count minimization has been critical but switches to all in an OEM-dominated sector?

We hear about cancellations, if true, well after AMD has done so. This would mean that they altered their plans an are possibly bring another design to the market. Seriously, they may have cancelled it two years ago, and we could just be getting hints that that happened now. All the semi-ODMs have learned how to keep a real tight lid on the details of their designs compared to 20 or even 10 years ago.If STX3 is indeed being canceled, that would be pretty bad cause Intel is coming strong with Lunar Lake targeting ultraportables. So far, Lunar Lake is pretty much confirmed to have 4P+4E designs with Battlemage grahics engine that made by TSMC N3, the specs match with STX3. So I would hope AMD resume the designs

The advantage is without question but that's not the point I'm getting at.Removing L3 from the main CCD die and increasing the size of L2 would not grow the die. It may even shrink it.

Sharing the L2 by making the other L2's core's L2s victim caches would improve utilization of the L2s and simulate some of the benefits of L3.

The 5000 X3D chiplets only amount to ~3-5W; the ones for 7000 X3D shouldn't be too far off. So their specific TDP was never a major problem but their voltage sensitivity and added heat insulation of the CCD due to being on top.Yeah, 120W does seem high, even 16-core Zen4 7945HX only requires 75W. Besides high clocks, reasons that I can think of are additional 128-bit memory bus (that would require 32-bit x 4) and huge amount of caches (FYI, M2 Pro has total L2+L3 cache of 60MB, STX Halo has 64MB total cache excluding L2 cache of each CPU cores, I would assume at least 16MB L2 caches, so total cache of Halo would be at least 80MB). That's why I don't believe of 96MB rumors unless Zen5/5c has 2MB of L2 cache each...

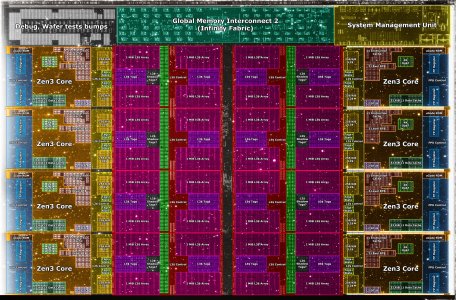

Each 'slice' of Zen4 on die L3$ is more than comparable in area with the cores themselves in this die shot:Removing L3 from the main CCD die and increasing the size of L2 would not grow the die. It may even shrink it.

Don't believe it for a second.surely there's another hapless engineer from amd @ linked in who's listed everything in his or her profile going back to their childhoold limeade stand.

Zen 5 in post silicon bring upDon't believe it for a second.

It came so long after Zen6 would have started its initial design, and Zen5 will be into prefab heavy prep at this point, possibly even very early engineering samples.

AMD just stealth released the info, and it doesn't really compromise anything, just creates futur buzz.

Assuming that the information told by AdoredTV is true regarding the L2 cache testing, it seems weird to me for AMD to actually test monolithic chips with different L2 sizes, considering the large design and mask costs associated just for R&D.2 takeaways for me:

- the new bus, that can scale to 16 unified cores in a single CCD.

- larger L2 without latency penalty being possible in future cores

Two of those combined lead me to believe that AMD plans on dropping L3 entirely from future generations of processors. Unknown if it will be Zen 5 or Zen 6.

you overestimate the common sense of engineers even veterans who don't know how a platform works. any person in the know can figure out what to get from info posted. The linkedin profile was nothing interesting. we've seen what lazy self awareness and security can do to any company. On the other hands, those who want to make a lil green will steal slowly over time. the list of people whom I've worked with over my career who've been arrested, tried and sometimes jailed grows every 4-5 years. some pass through the cracks.Don't believe it for a second.

It came so long after Zen6 would have started its initial design, and Zen5 will be into prefab heavy prep at this point, possibly even very early engineering samples.

AMD just stealth released the info, and it doesn't really compromise anything, just creates futur buzz.

Removing L3 from the main CCD die and increasing the size of L2 would not grow the die. It may even shrink it.

Sharing the L2 by making the other L2's core's L2s victim caches would improve utilization of the L2s and simulate some of the benefits of L3.

More like he predicted either slc (see apple) or l4 cache.Sorry, it's just that I was reading Anand's Phenom II review and that was this like: "Carrying that further, we may even see future CPUs with more cores add a forth level of cache.".

Anand predicted V-Cache!

yeah cause the v cache is a bit of l3 slapped onto the core chiplet connected by tsvs. what I don't get is the prior explorations of l4$ by intel were on systems where it was for the igpu and done with edram. from the mtl leaks a week ago it said intel's new approach is where the gpu is blocked from using the l4$, but from my own historic knowledge on l4$ on x86 is that $ level is largely useless. has intel made a breakthrough because all I've seen regarding this new approach is criticisms.More like he predicted either slc (see apple) or l4 cache.

www.notebookcheck.net

www.notebookcheck.net