- Mar 3, 2017

- 1,779

- 6,798

- 136

Uhh....the M1 air macs sold like hot cakes on release and still do now everywhereThey can.

Like, even Intel is making LNL-M.

But there's no market for it.

I don’t think that’s really true. The Lenovo p14s G2 AMD and p16s G2 AMD are good examples. Depending on configuration, 10 to 16 hours of battery life watching videos. The power limit is only slightly reduced when on battery.Wake me up when AMD can make an M1 competitor. Yes, I said M1. A SoC that can go into something as thin and small as a Macbook Air, fanless, 20 hours of battery life, extremely snappy, and performs the same plugged in or on battery.

In 2024, 3+ years after the M1, AMD is still no where close.

That's because it was a usable $999 macbook and not really the SoC part of it.Uhh....the M1 air macs sold like hot cakes on release and still do now everywhere

This confirms MLID has been supplied by real slides for some time.Leak is confirmed by GCC patch.

...

Quite surprised with 4x decode. I hope it there is future update not that it is still at 4 wide decode.

i do believe we moved to 41% bro , get it right .Zen 5 IPC gain: 32%

Source: adroc_thurston (trust me bro)

That's Sonoma Valley and it is sorts far off.Would be interesting to see what a pure Zen 5c based laptop could do.

Seems the slides are legit indeed.This confirms MLID has been supplied by real slides for some time.

The 4 decode with a big uop cache carried on?

I think going beyond four with the number of transistors and the smarts we have in our branch predictor, and the ability to feed it worked fine. But we are going to go wider, you're going to see us go wider, and to be efficient, we'll have the transistors around the front end of the machine to make it the right architectural decision.

i assume if its dual decode , and each "stream" is max 4 wide then compilers don't need to care.Seems the slides are legit indeed.

Basically whatever Mike Clark's remarked about Zen's future are materializing, of course since he is the CPU Chief.

But the decode is still not clear, now from the patches still at four.

- Bigger CCXs.

- Wider Frontend

- Xilinx IP integration

The patches are probably not final and they even mentioned they would update it going forward.

Zen 4 scheduler model did not change since 2022 for instance.

Mike did make the remark below when asked about wider decode.

I am interested in the decode width and how they implemented it, lots of patents point towards Tremont style dual decode.

Whatever it may be, they would have modelled it well enough and if they added lots of execution ports they would need to increase the decode width/op cache.

It's the best selling laptop in the world.That's because it was a usable $999 macbook and not really the SoC part of it.

There's really not a market for tablet parts otherwise.

How great is Mike Papermaster?

Is he on the same league as the likes of Jim Keller?

1. This laptop isn't fanless.I don’t think that’s really true. The Lenovo p14s G2 AMD and p16s G2 AMD are good examples. Depending on configuration, 10 to 16 hours of battery life watching videos. The power limit is only slightly reduced when on battery.

Full load will drain the battery faster, yeah, but it also will get way more work done with 8 P cores. Integrated graphics are on the level of a 2050

I’d say they are quite close already. A lot of the problem though is laptop OEMs but they seem to be catching on to the fact that people want Macbook level battery life on PCs too. Another problem is Windows vs OS X. Did you ever load Windows on an Intel Mac via bootcamp and compare battery life, even with all the right drivers? Not great

Edit: Meant to link reviews

These are Zen 4 notebooks so if Zen 5 offers any further efficiency improvements I don’t think it will be as hard as you think to close the gap

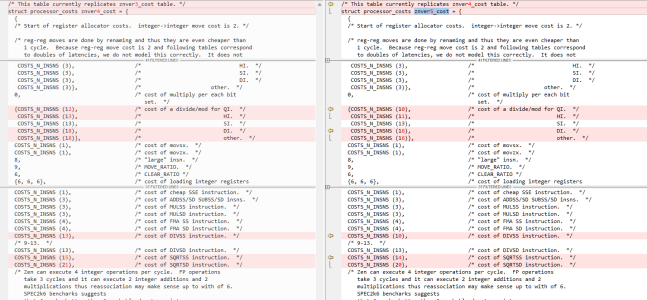

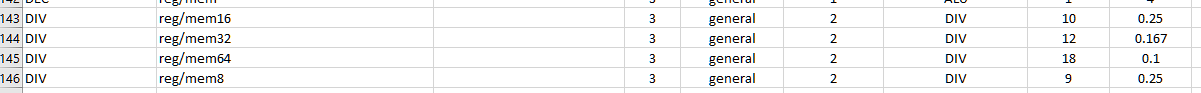

One thing which I am wondering is that znver5_cost table is aligned with the instruction construction in znver5.md in terms default latency for 8b/16b/32b/64b divisions. Comparing the znver4.md to znver5.md makes it seems as if there are regressions here but not in the scheduling costs table.

- cost of a divide/mod for

- QI: 12 -> 10

- HI: 13 -> 11

- SI: 13 (no change)

- DI: 18 -> 16

- Other: 18 -> 16

- cost of DIVSS instruction: 13 -> 10

- cost of DIVSD instruction: 13 (no change)

- cost of SQRTSS instruction: 15 -> 14

- cost of SQRTSD instruction: 21 -> 20

What will this be used for on Zen5 DT?Xilinx IP integration

Ah. The two Mikes are confusing. One is a Clark and the other is a Papermaster!Mike Clarke ,

he was/is an architect from pre Zen for AMD , and was one of the people who was in Jim kellers inner circle while the convinced the rest of AMD they could actually build Zen1. He now does the CPU road map and doesnt focus on specific cores now.

According to Apple who once recruited him, and from their own words, he has immense knowledge in large systems design and semiconductors physics, i guess that you re hugely underestimating the man.How great is Mike Papermaster?

Is he on the same league as the likes of Jim Keller?

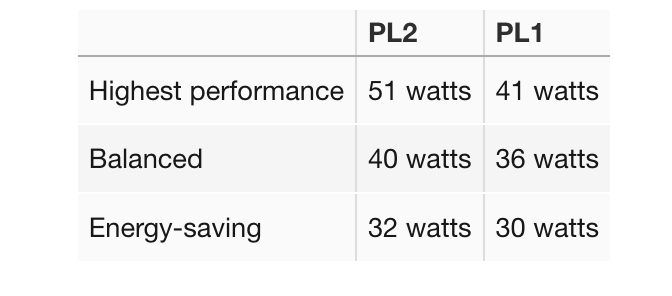

Ok, but I don’t think users care about any of that. It might not be fanless but it’s quiet. Geekbench 6 sucks and doesn't represent true MT performance. Nobody cares how many peak watts it uses (and that may not be the flex you think it is since the M1 only has 4 P cores). I’m sure it doesn’t use 51 W in ST, or the battery life would be garbage. And once you get past “all day” / 8 hour light usage battery life I don’t think many people care whether its 10 or 20 hours.1. This laptop isn't fanless.

2. The CPU goes up to 51 watts. On the M1 Air, the CPU only goes up to 10w.

View attachment 93644

3. Even though the 7840U uses 51watts, it still loses in GB6 ST and barely wins in GB6 MT - while using up to 5x more power.

4. This thing is $2,200 compared to $750 for M1 Air.

Like I said, AMD still can't match the M1 3.5 years ago. I doubt the even Zen5 can match the M1 in per/watt. AMD is about 3-5x behind in efficiency. Zen5 isn't going to make much of a difference. AMD needs to go back to the drawing board if it wants to compete against Apple, and soon Qualcomm as well.

No. It's Mark Papermaster.Ah. The two Mikes are confusing. One is a Clark and the other is a Papermaster!

As much as I would LOVE for you to be right, I'm afraid it's true that OEMs actually don't really want M1 style products targeting lower TDPs, and LNL is a perfect example of that. Early on in the process OEM's complained that Intel wasn't letting them set power limits high enough, which is why max configurable TDP on LNL went up.Uhh....the M1 air macs sold like hot cakes on release and still do now everywhere

More HP probook styled laptops incoming, I got one with an i3 ice lake, it literally thermal throttles and I had to prop it out, clean vents and everythingAs much as I would LOVE for you to be right, I'm afraid it's true that OEMs actually don't really want M1 style products targeting lower TDPs, and LNL is a perfect example of that. Early on in the process OEM's complained that Intel wasn't letting them set power limits high enough, which is why max configurable TDP on LNL went up.

See. That's why these unsustainable boost clocks are not good.More HP probook styled laptops incoming, I got one with an i3 ice lake, it literally thermal throttles and I had to prop it out, clean vents and everything

As long as they let users set TDP in BIOS. The last Dell Latitude I tested had four power profiles in its BIOS and in the silent one, it hardly lost maybe 30% performance. I think it was Tiger Lake.More HP probook styled laptops incoming,

Got none for HPs thats why I'm never recommending that brand xD but nice thoughAs long as they let users set TDP in BIOS. The last Dell Latitude I tested had four power profiles in its BIOS and in the silent one, it hardly lost maybe 30% performance. I think it was Tiger Lake.