- Mar 3, 2017

- 1,779

- 6,798

- 136

Not really most of the large businesses (fortune 500 companies) I know do not provide macs for workers.What I mean is that Macs are still considered the go to solution for work.

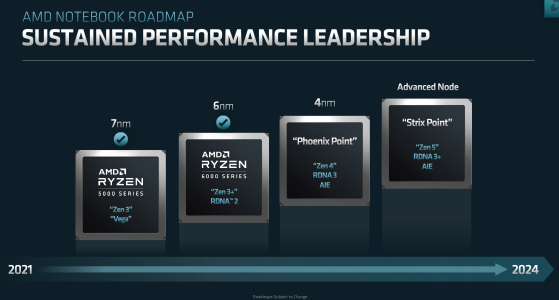

I was talking about normal Strix, not Halo. I mean what's the point of Strix when iGPU isn't better in games because of bandwidth Limit? You will have a CPU that destroys everything in Cinebench, but who needs that in a Laptop? AIE is also stronger but for 98% of consumers strix would be totally unnecessary compared to Pheonix or even Rembrandt.LNL just won't have the power available to be competitive against Strix Halo since it's geared more towards low power laptops with all day battery life.

Strix Halo supposedly will be disaggregated and have the Zen 5 gen's peak high tech packaging. No actual details publicly known though.Me and @BorisTheBlade82 been discussing advanced packaging and disaggregation for AMD Mobile SoCs for quite a while but seems each year it is still one generation away.

What is the consensus with Mobile SoC disaggregation for AMD. Is it Strix or Strix successor?

Or there is no Strix Successor, just Medusa for both DT and Mobile?

SoC tile with DDR5 MC like MTL + Memory Attached LLC on N6+ would really take integrated graphics to the next level.

RDNA4 also seems to rely heavily on MALL as can be seen from the LLVM MRs.

Strix Halo supposedly will be disaggregated and have the Zen 5 gen's peak high tech packaging. No actual details publicly known though.

From what I understand it was rumored to have it's own CCDs with only 16MB L3. Sounds really unlikely, but if it is true it's just a sign of how expensive it will be. Every die would be an exclusive tapeout only for this one product, quite contrary to what AMD is trying to do with their chiplets so far.I've been under the impression that Strix Halo is just Fire Range with a different IO die and packaging so that it has the 256-bit memory.

No LPDDR in the market can reach 10000depends on LPDDR clocks. 8840HS can run at 7500 MT/s, if Strix can run LPDDR memory at ~10000, it's gonna be fine

Isn't strix and strix halo Zen 5 ? I could be wrong, not questioning you, just asking. Is the below what they are talking about ? (STRIX POINT ??) the same ?Only wall of text i should be seeing is Zen5 in this thread.

I shouldn't be seeing Apple.

If you want to talk about Apple, there is a perfectly good apple thread.

But this is reserved for Zen5 and only Zen5.

Moderator Aigo

Strix Halo is already using chiplets, and I believe most of the Medusa lineup does too.Me and @BorisTheBlade82 been discussing advanced packaging and disaggregation for AMD Mobile SoCs for quite a while but seems each year it is still one generation away.

What is the consensus with Mobile SoC disaggregation for AMD. Is it Strix or Strix successor?

Or there is no Strix Successor, just Medusa for both DT and Mobile?

SoC tile with DDR5 MC like MTL + Memory Attached LLC on N6+ would really take integrated graphics to the next level.

RDNA4 also seems to rely heavily on MALL as can be seen from the LLVM MRs.

I could imagine AMD to follow the blueprint of MI300A. It was pretty surprising for me that they already included alternative D2D interfaces in the Zen4 CCD for which they basically just needed some different metal layers in order to enable them.From what I understand it was rumored to have it's own CCDs with only 16MB L3. Sounds really unlikely, but if it is true it's just a sign of how expensive it will be. Every die would be an exclusive tapeout only for this one product, quite contrary to what AMD is trying to do with their chiplets so far.

How much die area do those D2D interfaces take?I could imagine AMD to follow the blueprint of MI300A. It was pretty surprising for me that they already included alternative D2D interfaces in the Zen4 CCD for which they basically just needed some different metal layers in order to enable them.

The question for me is if they could use InFO-RDL or if they rely on capacity constrained CoWoS.

Curently it's believed to use the same RDL tech that Navi 31/32 usesThe question for me is if they could use InFO-RDL or if they rely on capacity constrained CoWoS.

They are tiny, which absolutely makes sense when you think about how much denser SoIC is than having to contact IFoP.How much die area do those D2D interfaces take?

Found it. Official slide from AMD. Look at the tiny blue squares compared to the GMI links.How much die area do those D2D interfaces take?

Hoping this as well. That would mean, they solved whatever issues prevented them from using that for MI300.Curently it's believed to use the same RDL tech that Navi 31/32 uses

I really don't know why you still continue with your narrative how Strix Point will be BW starved.

7500 not enough.I really don't know why you still continue with your narrative how Strix Point will be BW starved.

We already have fast enough LPDDR5X on the market. Even handhelds already use 7500mbps for Zen4.

AMD is not so stupid to put 16CU IGP inside but not be able to feed It, that just doesn't make sense.

Because AMDs APUs are Bandwith starved for 2 Years now?! It started with Rembrandt and now Phoenix is worse. Pheonix iGPU is clocked over 15% higher than Rembrandts and uses RDNA3, meanwhile it's not even 10% faster with same RAM and barely 15% with faster RAM. Also OEMs will always cheap out on faster RAM, so don't expect that every device comes with LPDDR5x-8533. New Tests of Desktop Versions also show that 7200 brings nearly no difference compared to 5200 (only about 7%). All this leads to the conclusion that Strix will be Bandwith starved to the moon.I really don't know why you still continue with your narrative how Strix Point will be BW starved.

We already have fast enough LPDDR5X on the market. Even handhelds already use 7500mbps for Zen4.

AMD is not so stupid to put 16CU IGP inside but not be able to feed It, that just doesn't make sense.

Also, 760M is just 15% slower than 780M while having 33% less CUs, than 780M.Because AMDs APUs are Bandwith starved for 2 Years now?! It started with Rembrandt and now Phoenix is worse. Pheonix iGPU is clocked over 15% higher than Rembrandts and uses RDNA3, meanwhile it's not even 10% faster with same RAM and barely 15% with faster RAM. Also OEMs will always cheap out on faster RAM, so don't expect that every device comes with LPDDR5x-8533. New Tests of Desktop Versions also show that 7200 brings nearly no difference compared to 5200 (only about 7%). All this leads to the conclusion that Strix will be Bandwith starved to the moon.

Why couldn't it be latency?If this is not memory starvation - I do not know what is.