- Mar 3, 2017

- 1,774

- 6,757

- 136

I think that's easy to see. If I was in charge of purchasing & configuring server racks for a major company that has used Intel for the past 20 years, would I risk my salary for the company to get better TCO? Even if I knew that the AMD product would be better in every way and just as reliable - I would still be fearful of getting blamed for anything that went wrong in the migration. Combine this with better availability for Intel processors and their willingness to accept much lower margins and it's easy to see people taking the path of least resistance.This is more of a comment, but also a little bit of a question. And yes I know about OEMS and idiot IT managers, BUT...

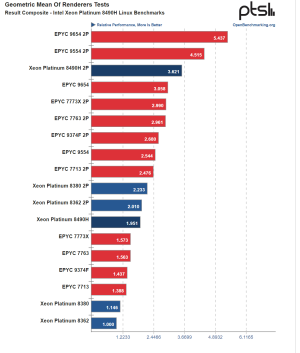

With AMD as king in performance and perf/watt and perf/$$ for at least 4 years, and with Genoa,Genoa-X and Bergamo do crushing anything Intel has, or is going to release soon, how is it that they STILL can't get more market share. How long can Intels name keep them selling their crap server parts this far down the line ? This many years with crap ?

Edit: not to mention Zen 5 and Turin.....

Don't remember tbh. One of those chinese reviewers that actually test perf/watt unlike their western counterparts. Just google it lol.Who tested It?

LinkDon't remember tbh. One of those chinese reviewers that actually test perf/watt unlike their western counterparts. Just google it lol.

What is GNR ? what core ? how many ? what power ?GNR?

Redwood Cove, ~120 cores, 500W.What is GNR ? what core ? how many ? what power ?

Granite Rapids? ~120 cores IIRC, power same as Turin, 500 watts.What is GNR ? what core ? how many ? what power ?

People love comparing Bergamo and Sierra Forest in total MT performance as if people are really going to use it for that. What matters is how efficient they are per core or per core cluster at any given clock.the 144/288 e-cores CPU they are coming out with is DOA IMO. e-cores vs less cache but full power Zen 4 cores ? Like 2 to 1.

Doesn't Bergamo beat that ? at WAY less power usage ?Redwood Cove, 120 cores (could be slightly more depending how much is disabled per tile) 500W.

To be honest, I don't know. I don't expect GNR to outperform Turin outside of AMX accelerated tasks.Doesn't Bergamo beat that ? at WAY less power usage ?

I just saw the post above this, but Turn at 500 watts is most likely WAY faster. And I will wait for reviews on Sierra forest as to how fast and efficient.

And then of course, does GNR support avx-512 ?To be honest, I don't know. I don't expect GNR to outperform Turin outside of AMX accelerated tasks.

Granite Rapids.What is GNR ?

Well yea, they're exact same socket power (360 vs 350W).People love comparing Bergamo and Sierra Forest in total MT performance as if people are really going to use it for that

It just doesn't scale to 64c*2p systems.

Yeah it would but really depends on the workload.

No, it'll load as many threads as it could and cap out the perf.then this benchmark should be a massive outlier in favor of the Zen5 system, not a massive outlier against it.

We're not talking a single nT app running on whole socket.That would only help MT because of Amdahl's law.

No, it'll load as many threads as it could and cap out the perf.

We're not talking a single nT app running on whole socket.

They're separate things instanced a zillion times over.

It loads the threads sequentially until it hits the socket cap.So what happens when an application doesn't scale well to 256T

Yes, just read SPECcpu 2017 documentation.And are all those instances single threaded?

I mean I just posted this, but no one is using Bergamo for just raw MT perf. Oh sure, technically, Bergamo even beats Genoa in raw MT perf, but again, even AMD is calling these cloud processors, not HPC processors. The reason why is pretty obvious.Doesn't Bergamo beat that ? at WAY less power usage ?

Well, lets do some rough, simplistic math based on rumors.I just saw the post above this, but Turn at 500 watts is most likely WAY faster.

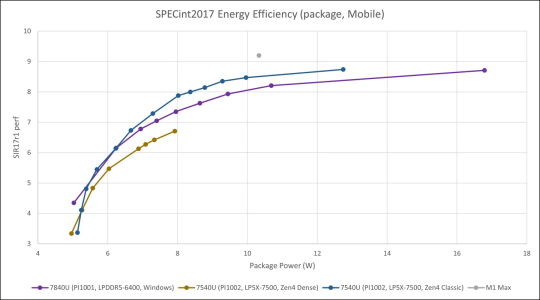

We have straight up power curves too, finally decided to stop being lazy and just search it up lolIt's freq/voltage curve - not perf/w. Dense core has less static and dynamic power variables so it's more efficient at given voltage. Zen4 &c efficiency switch point is somewhere around 3GHz, which quick calculation gives approximation that it's combined dynamic/static capacitance at that 3GHz is about 2/3 of regular core.

I mean I just posted this, but no one is using Bergamo for just raw MT perf. Oh sure, technically, Bergamo even beats Genoa in raw MT perf, but again, even AMD is calling these cloud processors, not HPC processors. The reason why is pretty obvious.

I think this is basically what I am saying. AMD rules servers in every respect today, and for the foreseeable future. I saw the post about the IT manager thinking "I will never get fired for buying Intel", but I am so sick of that. I can not believe for over 5 years, and with power getting more and more expensive that they won't rethink. They could get a raise if they told their manager "look, this is 30% more efficient on power and is faster". Not to mention in data center, the amount is arguable, but 1 watt saved = 2-3 watts saved due to AC and to APS support.<snip>

In which case we get Turin being 48% more performant than GNR, which doesn't shrink the gap between how much SPR loses to Genoa... but it drastically improves the efficiency gap since both of these CPUs will be at 500 watts. Me personally? I think the gap is going to be closer to ~30%, but we will see.

(final disclaimer, ik this is a massively oversimplified projection based on leaks, not including stuff like memory bandwidth or SMT vs 1T, etc etc, but this was just for fun anyway

Intel's just going to continue selling stuff dirt cheap. Gonna be fun to see how they manage to do that with insanely expensive GNR, that prob uses more silicon than Turin while also using a "newer" node.I think this is basically what I am saying. AMD rules servers in every respect today, and for the foreseeable future. I saw the post about the IT manager thinking "I will never get fired for buying Intel", but I am so sick of that. I can not believe for over 5 years, and with power getting more and more expensive that they won't rethink. They could get a raise if they told their manager "look, this is 30% more efficient on power and is faster". Not to mention in data center, the amount is arguable, but 1 watt saved = 2-3 watts saved due to AC and to APS support.

It loads the threads sequentially until it hits the socket cap.

Yes, just read SPECcpu 2017 documentation.

What about x(3d) factor? That is big unknown.Wow you've almost nailed Turin perf.

Congrats.

Again, cinememe can't scale well on server CPUs since it runs out of tiles.Which isn't relevant. The worse that additional threads perform, the better the architecture that relies less on SMT for its total throughput should come off.

Socket perf projection numbers from every vendor out there tend to be SIR2017 rate n.So now we're just talking about SPEC

Again, cinememe can't scale well on server CPUs since it runs out of tiles.

Only if it loads 1c/1t increments(it doesn't, tiles are loaded sequentially and contained to one socket).Again, that's the exact scenario that will disproportionately benefit the architecture that gains a massive non-SMT uplift at the expense of SMT yield, except that's not what the leak is showing.