- Mar 3, 2017

- 1,779

- 6,798

- 136

+32% ipc w/ -7% clock (400mhz, from 5.7ghz to 5.3ghz ) will yield 25% st uplift. Still hoping for more to be honest. You mentioned before zen 5 was designed to compete with arrow lake. Would you say amd have just done just that? Surely the arrow lake AMD have in mind is quite a tad faster than that appeared in the intel projection slide.Yeah.

Late March or April.

Dawg it was a Daytona issue.

Marketshare is irrelevant if you're forcing a price war against an IDM and tanking the margin.

Yeah, 2024 was supposed to be a party.You mentioned before zen 5 was designed to compete with arrow lake

At least SPR has horrible cost structure.Before AMD can eat Intel's market share, they'll have to eat their margins.

If there’s a 25% 1T perf increase why wouldn’t it be a party?Yeah, 2024 was supposed to be a party.

That would be absolutely bonkers if it turned out that way. If I were looking to buy AMD I’d be really happy with that outcome.+32% ipc w/ -7% clock (400mhz, from 5.7ghz to 5.3ghz ) will yield 25% st uplift. Still hoping for more to be honest.

Lisa's gonna take my kidneys away.If there’s a 25% 1T perf increase why wouldn’t it be a party

25% 1t is kinda the bare minimum expectation for an AMD tock.That would be absolutely bonkers if it turned out that way.

They're the same.What about vcache chips

Kinda the opposite, Zen5 is better at coping with bad memory setups.I have feeling that we will see more gains than with previous Zen gens

Nothing.Boy what will Zen6 with new package do in this regard

Not sure what is meant by this, if it’s in reference to the stock / business fundamentals I don’t see anything in 2024 that would spell doom but I don’t have any special insight into the company.Lisa's gonna take my kidneys away.

ARL-S will allegedly have an uncharacteristically weak 1T perf increase. So if there was ever a time to miss the 30% 1T target it’d be in 2024.25% 1t is kinda the bare minimum expectation for an AMD tock.

Not sure what is meant by this, if it’s in reference to the stock / business fundamentals I don’t see anything in 2024 that would spell doom but I don’t have any special insight into the company

I don’t think that’s it. Zen 5 shouldn’t be that much more expensive than Zen 4.It means he thinks it will be very expensive.

Marketshare is irrelevant if you're forcing a price war against an IDM and tanking the margin.

More expensive node, larger die (probably, zen 4 CCD is tiny) and a potentially materially relevant performance advantage all point to AMD trying to hike prices again like they did with Zen 2 to Zen 3.I don’t think that’s it. Zen 5 shouldn’t be that much more expensive than Zen 4.

Increased IPC increases power consumption.For clocks and performance, not IPC.

AMD announces new mobile parts every January, so we should get mobile Zen 5 at minimum.March or April seems optimistic to me. AMD never specified the exact half year, they just said 2024. This is usually an indication for a H2 launch rather than a H1 launch. I don't think we are getting Zen 5 in H1 of 2024.

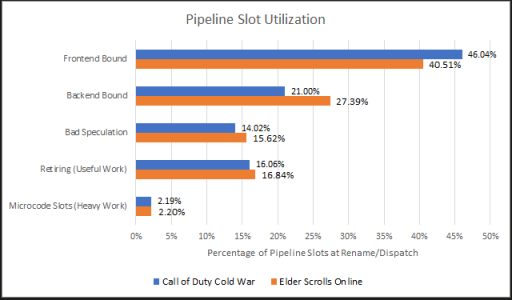

Both profiles show being frontend-bound in nearly 50%. This seems to be a common pattern. Zen 5 continues the existing trend - Zen 1 added uop cache, Zen 2 doubled the uop cache size, Zen 3 +50% wider dispatch, Zen 4 over 50+% of the uop cache, etc."Both gaming workloads are overwhelmingly frontend bound. They’re significantly backend bound as well, and lose further throughput from bad speculation. Useful work occupies a relatively minor proportion of available pipeline slots, explaining the low IPC."

It's not just the mircoop cache that gets a boost in Zen 5 : AMD states they reworked the front end (re-pipelined the front end). It's a major redesign, but we have no details yet.Both profiles show being frontend-bound in nearly 50%. This seems to be a common pattern. Zen 5 continues the existing trend - Zen 1 added uop cache, Zen 2 doubled the uop cache size, Zen 3 +50% wider dispatch, Zen 4 over 50+% of the uop cache, etc.

I may have missed this, but were there any assumptions on whether Zen 6 will require a new socket?

Just curious of what actual AM5 lifespan is.

AMD announces new mobile parts every January, so we should get mobile Zen 5 at minimum.

Intel is dropping Raptor Lake Refresh now and Arrow Lake H2 2024. If Zen 5 is a zinger, AMD will want to release it ASAP, that way they can have at least a year of market leadership.

The thing is this: In each pipelined system, there are bottlenecks - be it a production line in a factory or a CPU. These bottlenecks might shift depending on the workload, which makes it important to define "common" workloads as optimization targets. And whenever you widen one bottleneck, another one will arise, that becomes the tightest part of the system.Not sure if this has already been posted: https://chipsandcheese.com/2023/09/06/hot-chips-2023-characterizing-gaming-workloads-on-zen-4/

View attachment 86560

"Both gaming workloads are overwhelmingly frontend bound. They’re significantly backend bound as well, and lose further throughput from bad speculation. Useful work occupies a relatively minor proportion of available pipeline slots, explaining the low IPC."

Zen 5 main design goals:

View attachment 86562

Looks like Zen 5 will address the main bottlenecks in Zen 4, at least when gaming is concerned. Fun times for Arrow Lake

How else they would handle 4 loads per clock? That's pretty much implied.Looks like there is +1 AGU as well besides what I summarized earlier.

Increased IPC increases power consumption.

You guys are laying into @adroc_thurston like crazy to the point you go on the attack for nothing. I am just as critical of someone with no credibility showing up and making grandiose claims as the next person, but this IS a discussion and speculation thread, and the results WILL bear themselves out eventually. If he is right, he will be right, if he is wrong, he will be wrong.