Covfefe

Member

Copying and pasting my comment from the Intel thread (oops).

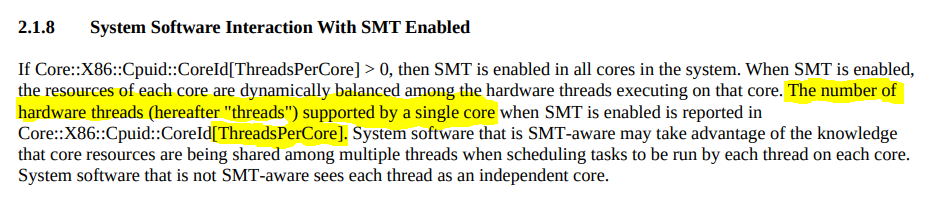

AMD uses "statically partitioned" to refer to a resource that can never be used 100% by a single thread.

AMD uses "competitively shared" to mean that a single thread can use 100% of a resource, but when SMT is active the two threads have to split it.

AMD calls the 50/50 split (when SMT is active) for the micro-op cache competitive sharing, not static partitioning.

AMD uses "statically partitioned" to refer to a resource that can never be used 100% by a single thread.

AMD uses "competitively shared" to mean that a single thread can use 100% of a resource, but when SMT is active the two threads have to split it.

AMD calls the 50/50 split (when SMT is active) for the micro-op cache competitive sharing, not static partitioning.