DisEnchantment

Golden Member

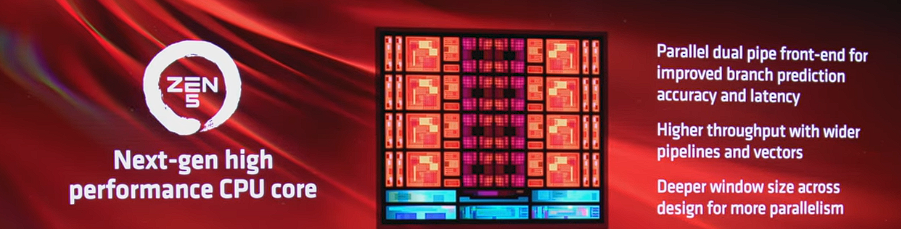

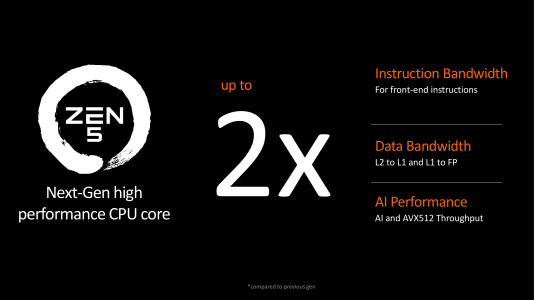

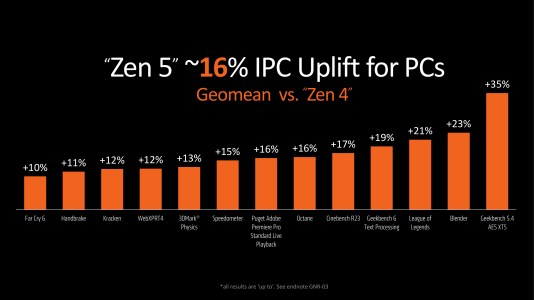

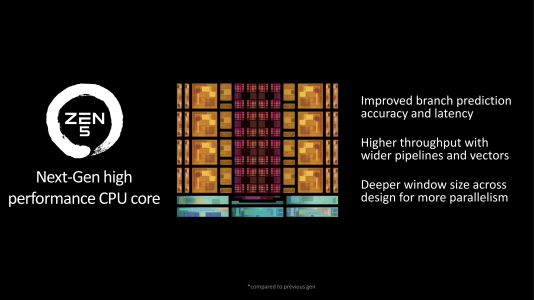

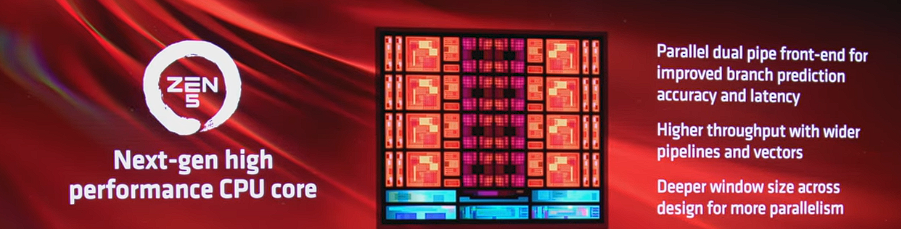

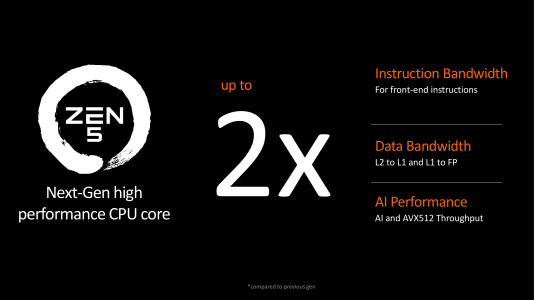

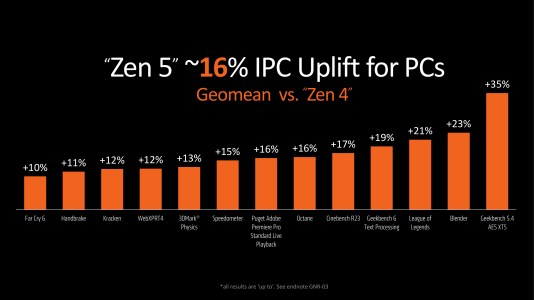

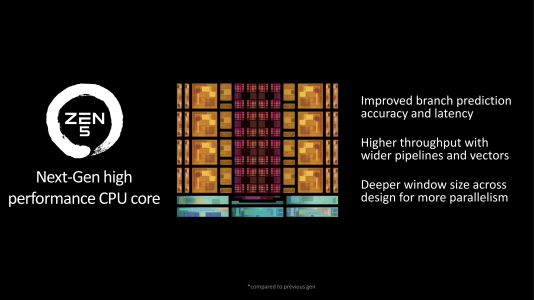

Since we have the official unveil done, would be a good time to discuss on the Architecture and technical specifications of the Zen 5 Core.

More details will be added once they are public like die size, architecture details etc.

---------------------------------------------------------------------------------------

More details will be added once they are public like die size, architecture details etc.

---------------------------------------------------------------------------------------

- No Market share discussion

- No Leaks

- No speculation unrelated to publicly released technical materials/patches/manuals etc.

Last edited: