- Mar 27, 2009

- 12,968

- 221

- 106

Another reference point to take a look at:

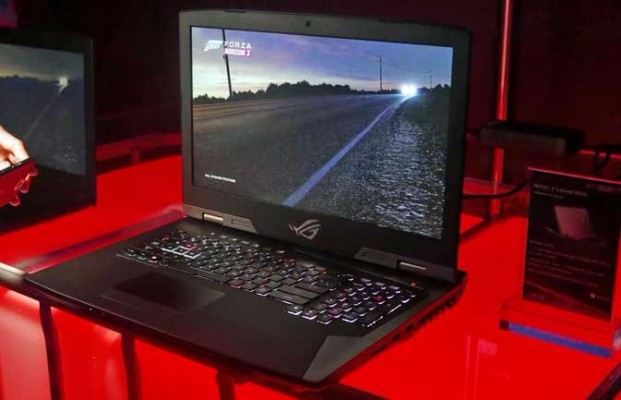

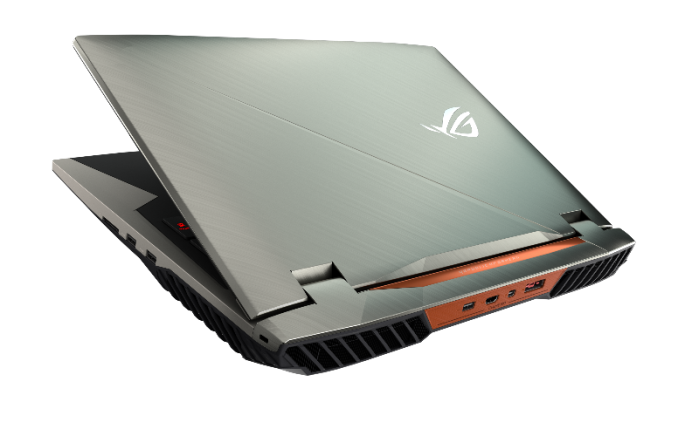

Asus ROG Strix GL702ZC (This is a 17.3" 7.04 lb laptop with a 65W Ryzen AM4 CPU (using B350 chipset) and a mobile RX580 4GB* in it)

https://www.bit-tech.net/previews/t...preview-asus-rog-strix-gl702zc-benchmarked/1/

(NOTE: Ryzen 7 1700 is also available)

*Notebookcheck estimates the power consumption of the mobile RX580 to be around 89W.....so the 65W CPU and dGPU together would consume 154W.

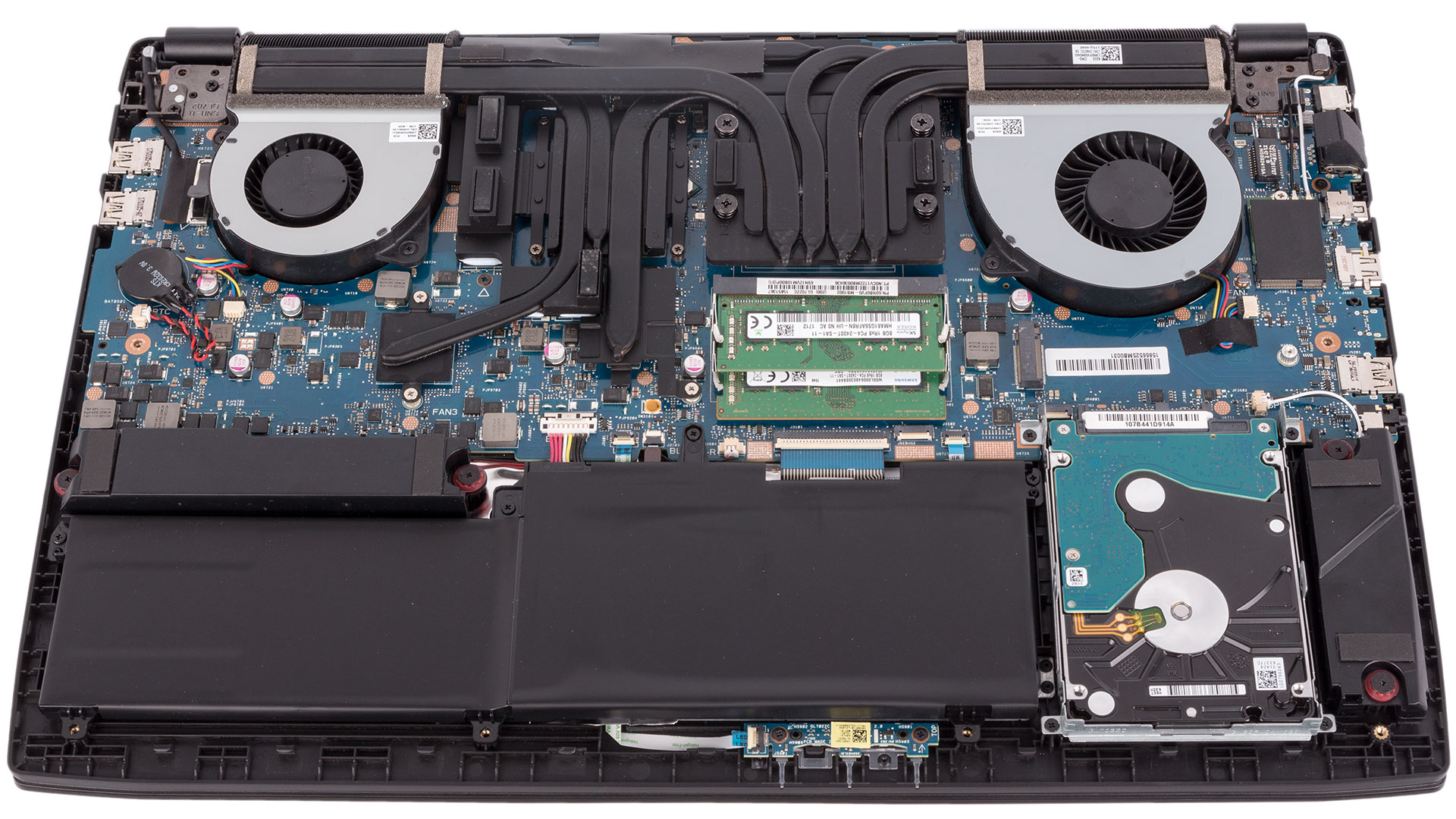

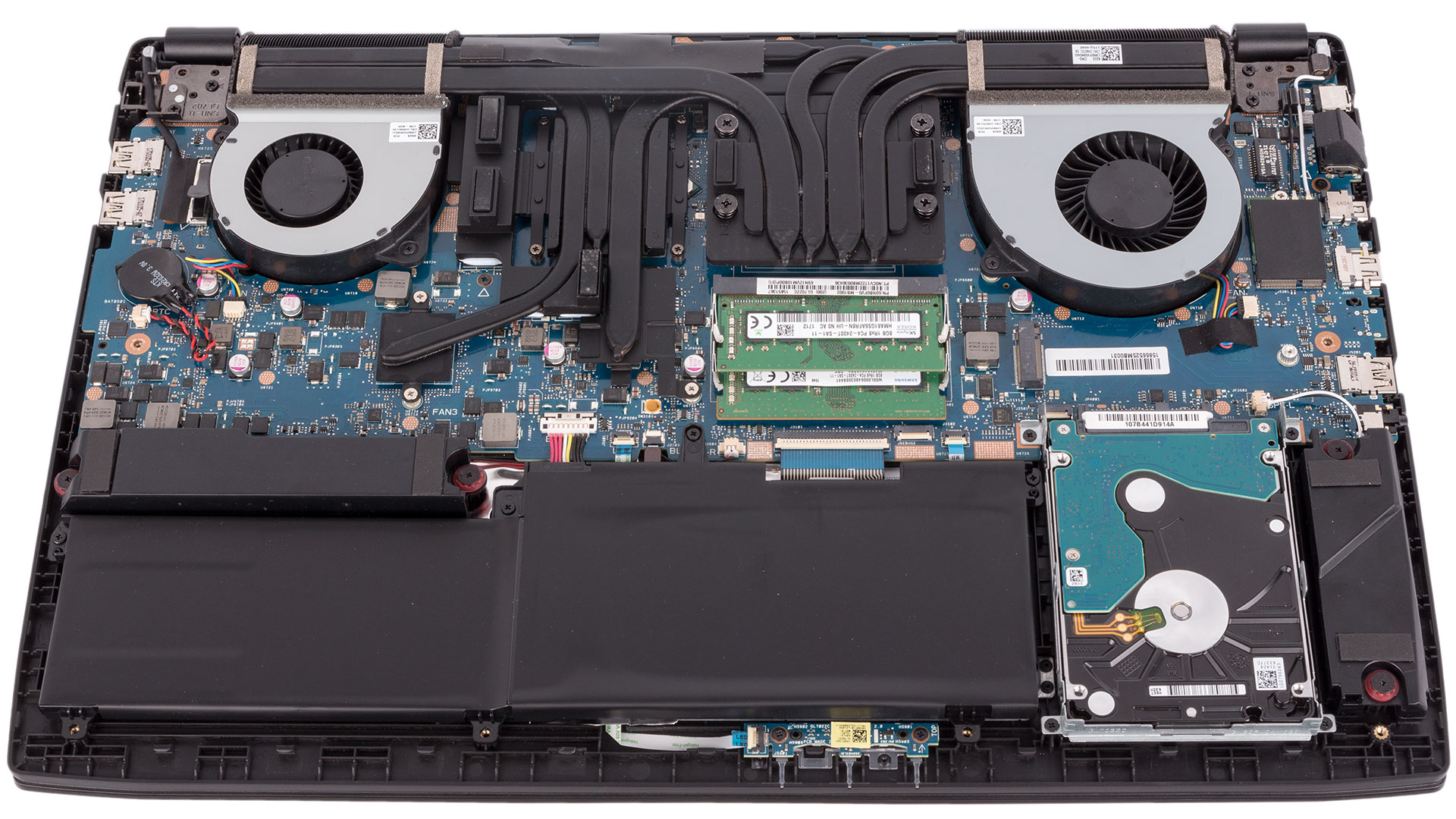

Here is what the cooling looks like:

Asus ROG Strix GL702ZC (This is a 17.3" 7.04 lb laptop with a 65W Ryzen AM4 CPU (using B350 chipset) and a mobile RX580 4GB* in it)

https://www.bit-tech.net/previews/t...preview-asus-rog-strix-gl702zc-benchmarked/1/

We didn’t have time to do a full tear-down, but hidden beneath the cooler is the six-core Ryzen 5 1600 CPU sporting its usual six cores. It carries all the same specs as the desktop part including 3.2GHz / 3.6GHz base and boost clocks. The TDP of this chip is a hefty 65W. The other component directly cooled is, of course, the Radeon RX 580 GPU and associated 4GB of GDDR5. The core is clocked at 1,077MHz, which is down from the 1,340MHz boost clock of the desktop part, but the memory is at the same 8Gbps as the desktop model.

(NOTE: Ryzen 7 1700 is also available)

*Notebookcheck estimates the power consumption of the mobile RX580 to be around 89W.....so the 65W CPU and dGPU together would consume 154W.

Meanwhile, the Radeon RX 580 should be around 90% the performance of an Nvidia GTX 1060, but will consume 10-11% more power.

Here is what the cooling looks like: