- Apr 27, 2000

- 23,204

- 13,289

- 136

Looks like SiFive is going to sell a RISC-V SBC that has four U7 cores (the 4c U7 core complex is designated U74-MC). It's also got an S7 core in it, though I haven't yet figured out what that does. Article:

liliputing.com

liliputing.com

Price definitely isn't right. If you look at the U7 core:

Also please reference:

www.cnx-software.com

www.cnx-software.com

The U7 core leaves a lot to be desired. If I were going to buy a development platform to deploy software on other systems, I would want most (if not all) ISA extensions available, so I would have the ability to target nearly any present or future RISC-V system. With ARM I can get a Graviton2 instance and write ARM software that will run on any ARMv8 SoC out there - assuming it's running Linux. The U74-MC complex doesn't get you any SIMD/vector math, for example. ARM has had NEON for years.

DockFrame is a modular USB-C dock that supports Framework Expansion cards - Liliputing

DockFrame is a modular USB-C dock that supports Framework Expansion cards

Price definitely isn't right. If you look at the U7 core:

Also please reference:

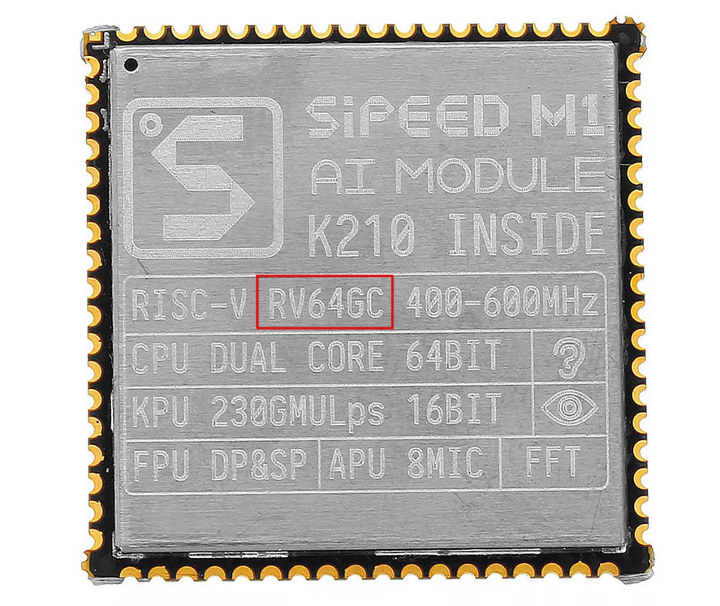

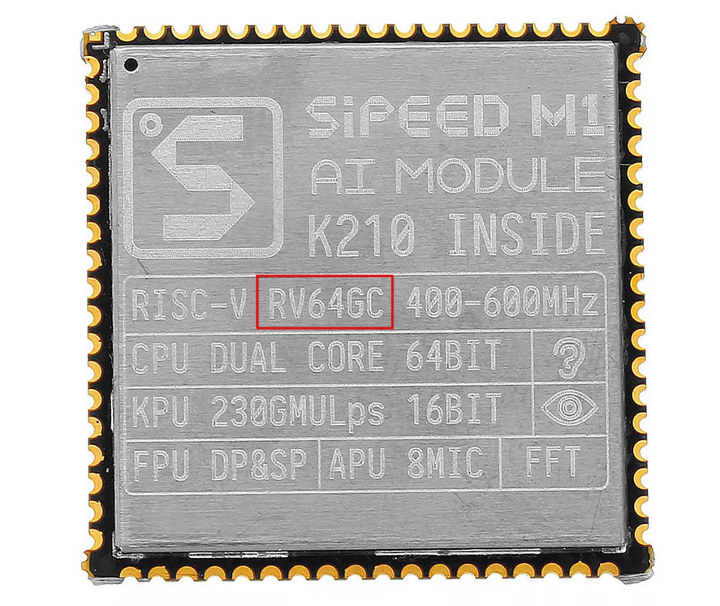

RISC-V Bases and Extensions Explained - CNX Software

RISC-V ISA nonemclature is comprised of RISC-V bases and RISC-V extensions. In this post, we explains how to decode RISC-V core architecture names.

www.cnx-software.com

www.cnx-software.com

The U7 core leaves a lot to be desired. If I were going to buy a development platform to deploy software on other systems, I would want most (if not all) ISA extensions available, so I would have the ability to target nearly any present or future RISC-V system. With ARM I can get a Graviton2 instance and write ARM software that will run on any ARMv8 SoC out there - assuming it's running Linux. The U74-MC complex doesn't get you any SIMD/vector math, for example. ARM has had NEON for years.