Discussion RDNA 5 / UDNA (CDNA Next) speculation

Page 23 - Seeking answers? Join the AnandTech community: where nearly half-a-million members share solutions and discuss the latest tech.

You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

- Apr 28, 2024

- 2,181

- 2,814

- 96

Along with xbox next yearwhen is it going to launch cause i know for sure it will be on N3E/P.

Xbox nov

RDNA 5 probably dec-31st

Xbox I don't have high hopes for next year lol ngl.Along with xbox next year

Xbox nov

RDNA 5 probably dec-31st

GodisanAtheist

Diamond Member

- Nov 16, 2006

- 8,480

- 9,890

- 136

True, but almost certainly not abandoning IF caching schemes. GDDR7 alone cannot replace the bandwidth amplification of a large cache.

- New GDDR probably means they can shrink IC and claw back some die space though.

IC is a good crutch while AMD uses GDDR6, while NV went with more exotic RAM.

GDDR7 won't eliminate the need for IC, but will likely minimize it.

"Magnus" could use 384bit + 48 MByte IF$ instead of 96 MByte. In the end a tradeoff between effective bandwidth and amount of VRAM.

IC was used effectively even when NVIDIA was also on GDDR6.- New GDDR probably means they can shrink IC and claw back some die space though.

IC is a good crutch while AMD uses GDDR6, while NV went with more exotic RAM.

GDDR7 won't eliminate the need for IC, but will likely minimize it.

I don't think cache can reduce the need for "amount of VRAM"."Magnus" could use 384bit + 48 MByte IF$ instead of 96 MByte. In the end a tradeoff between effective bandwidth and amount of VRAM.

It amplifies bandwidth, so allows a smaller bus width. We should remember, the space needed for memory controllers is reduced, so this needs to be factored in the total cache+memory controllers area. The penalty might be a lot smaller than we think as logic shrinks faster than analog. Reduced power is another benefit.

itsmydamnation

Diamond Member

- Feb 6, 2011

- 3,114

- 3,965

- 136

Also rtrt drives latency , reducing cache will hurt rtrt regardless of overall bandwidth.

IC is also more power efficient than VRAM access, this was one big factor of RDNA2's massive perf/W improvement.

48MB might be enough for 80 CUs running at more modest clocks in a console (remember previous console SoCs had no GPU IC at all), but for a 96 CU desktop GPU with 20+% higher CU IPC and clocked to 3+ GHz, 96MB might be necessary to hit their perf targets at 4K and RT/PT in general, despite GDDR7.

FWIW, Nvidia didn't back down on their L2 sizes with Blackwell despite GDDR7 either, and NV is no less margin-oriented than AMD.

48MB might be enough for 80 CUs running at more modest clocks in a console (remember previous console SoCs had no GPU IC at all), but for a 96 CU desktop GPU with 20+% higher CU IPC and clocked to 3+ GHz, 96MB might be necessary to hit their perf targets at 4K and RT/PT in general, despite GDDR7.

FWIW, Nvidia didn't back down on their L2 sizes with Blackwell despite GDDR7 either, and NV is no less margin-oriented than AMD.

No, IF$ cannot reduce the amount of needed VRAM.I don't think cache can reduce the need for "amount of VRAM".

It amplifies bandwidth, so allows a smaller bus width.

But if you want a certain amount of VRAM, you need to have a certain bus width. If you widen the bus, you can reduce the size of IF$ without running into bandwidth bottlenecks. That's why I was talking about a tradeoff in this regard.

You could go the other way round: 128bit and 512MByte IF$. But the narrow bus width then limits the maximum VRAM capacity.

Other topics like energy efficiency and effective memory latency will get worse with wider bus width and less IF$. If those parameters are not your primary concern, a widened bus can be the right choice.

adroc_thurston

Diamond Member

- Jul 2, 2023

- 8,204

- 10,949

- 106

No, the massive RDNA2 p/w bump was just going off the physical design.this was one big factor of RDNA2's massive perf/W improvement.

MALL allowed them to ship a 256b flagship-ish parts and it made NV really, really scared.

Fortunately, RDNA3 did not go so well.

Yes, but it's not a magic bullet for the same reason that people are bickering over the 8/16 GB cards issue at the moment.IC is also more power efficient than VRAM access, this was one big factor of RDNA2's massive perf/W improvement.

More efficient software techniques (virtual texturing etc) and hardware µArch can mitigate this need to a limited extent, but it won't ever go away.

If they ever get around to stacking HBM directly on the GPU (or under) it will also mitigate some of the power efficiency and latency issues from VRAM access.

ToTTenTranz

Senior member

- Feb 4, 2021

- 898

- 1,498

- 136

Truth be told, AMD has downscaled MALL-per-Performance a lot since RDNA2 already.GDDR7 won't eliminate the need for IC, but will likely minimize it.

N21 had a whopping 128MB IC, then N31 ~50% was faster with 96MB albeit with a wider IC and VRAM bus, and now N48 is ~50% faster than N21 with only 64MB and same VRAM bus width (though clocked 25% faster).

Cache area has also been practically stagnant across process nodes for a while and that is only changing after 3nm.The penalty might be a lot smaller than we think as logic shrinks faster than analog.

Most probably because Nvidia was also planning for Blackwell to clock a lot higher than it did in the end, resulting in overkill effective bandwidth.FWIW, Nvidia didn't back down on their L2 sizes with Blackwell despite GDDR7 either, and NV is no less margin-oriented than AMD.

It was their Vega/RDNA3 moment.

Truth be told, AMD has downscaled MALL-per-Performance a lot since RDNA2 already.

N21 had a whopping 128MB IC, then N31 ~50% was faster with 96MB albeit with a wider IC and VRAM bus, and now N48 is ~50% faster than N21 with only 64MB and same VRAM bus width (though clocked 25% faster).

That's because MALL/performance is a completely nonsense thing that doesn't matter!

You do not need a specific amount of MALL for specific amount of performance. You need a specific amount of MALL for a given target render resolution. It doesn't matter how complex your scene is or how much time you spend in your shaders, the main bandwidth amplification is about getting your render target fit in cache across frames, so it never needs to hit ram. The only meaningful measure is is MALL/resolution. This is why MALL wasn't a thing before, you couldn't provide enough for the target resolution until cache got cheap enough.

MALL has slightly decreased since introduction because AMD has gotten better at optimizing. Both with better FB compression, and by better excluding things from being cached in the MALL.

you can take that logic and shove it in the 8gb vram doesn't matter thread, these products should be built to perform as best as possible, period.You need a specific amount of MALL for a given target render resolution

itsmydamnation

Diamond Member

- Feb 6, 2011

- 3,114

- 3,965

- 136

really? you think a card faster than the 6900xt in 4k should have less less infinity cache because someone in marketing decided its not a 4k GPU?what? this makes no sense no matter what direction i approach it in

itsmydamnation

Diamond Member

- Feb 6, 2011

- 3,114

- 3,965

- 136

thats not how reality worksreally? you think a card faster than the 6900xt in 4k should have less less infinity cache because someone in marketing decided its not a 4k GPU?

adroc_thurston

Diamond Member

- Jul 2, 2023

- 8,204

- 10,949

- 106

Yeah that's how product planning/segmentation works.you think a card faster than the 6900xt in 4k should have less less infinity cache because someone in marketing decided its not a 4k GPU?

ToTTenTranz

Senior member

- Feb 4, 2021

- 898

- 1,498

- 136

I meant MALL per Performance Bracket. And it obviously matters to the engineers designing the chip and trying to balance cost (die area) towards a target selling price.That's because MALL/performance is a completely nonsense thing that doesn't matter!

Zero people said this.You do not need a specific amount of MALL for specific amount of performance.

You need a specific amount of MALL for a given target render resolution.

Yes. And for any resolution between FHD and 4K, N48 bests N21 with half the amount of MALL.

Not only that, the performance advantage of the 9070XT actually increases as resolution goes up, despite using half the MALL.

Considering AMD doubled the bus width per cell for RDNA3, we should expect around the same MALL bandwidth-per-clock in N48 versus N21.

Halving the amount of MALL for a faster-all-around-SKU isn't a slight decrease. It's a major one.MALL has slightly decreased since introduction because AMD has gotten better at optimizing.

This is the motive that leads to my initial statement, that AMD has significantly downsized the MALL per performance bracket since RDNA2.Both with better FB compression, and by better excluding things from being cached in the MALL.

Not sure why you thought that needed some kind of rebuttal.

Win2012R2

Golden Member

- Dec 5, 2024

- 1,288

- 1,343

- 96

384bit is 4k card, no chance cache goes so low"Magnus" could use 384bit + 48 MByte IF$ instead of 96 MByte. In the end a tradeoff between effective bandwidth and amount of VRAM.

Fortunately, RDNA3 did not go so well.

Why "fortunately"?

Attachments

Last edited:

SolidQ

Golden Member

- Jul 13, 2023

- 1,540

- 2,541

- 106

Next steam deck is RDNA5 apu?

www.tomsguide.com

www.tomsguide.com

Steam Deck 2 rumored to be in the works — and it may arrive with a massive AMD APU upgrade

Will Valve finally deliver a home console, too?

- Apr 28, 2024

- 2,181

- 2,814

- 96

I am guessing that valve will wait for 3nm to get cheap. However long that takesNext steam deck is RDNA5 apu?

Steam Deck 2 rumored to be in the works — and it may arrive with a massive AMD APU upgrade

Will Valve finally deliver a home console, too?www.tomsguide.com

Right now only 6nm & 7nm are cheap

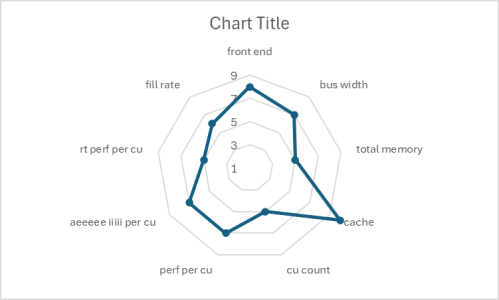

It's real but some of the numbers like CU count are slightly wrong (maybe intentionally to find out who leaks this).Mlid show some RDNA5 documents(don't know real or not)

SolidQ

Golden Member

- Jul 13, 2023

- 1,540

- 2,541

- 106

he saying one of AMD sources leak. instead 184 is 144CU?maybe intentionally to find out who leaks this

if slightly wrong, so they gonna try compete vs 6090 with near tripple CU compare to N48?

TRENDING THREADS

-

Discussion Zen 5 Speculation (EPYC Turin and Strix Point/Granite Ridge - Ryzen 9000)

- Started by DisEnchantment

- Replies: 25K

-

Discussion Intel Meteor, Arrow, Lunar & Panther Lakes + WCL Discussion Threads

- Started by Tigerick

- Replies: 24K

-

Discussion Intel current and future Lakes & Rapids thread

- Started by TheF34RChannel

- Replies: 23K

-

-

AnandTech is part of Future plc, an international media group and leading digital publisher. Visit our corporate site.

© Future Publishing Limited Quay House, The Ambury, Bath BA1 1UA. All rights reserved. England and Wales company registration number 2008885.