- Nov 14, 2011

- 10,497

- 5,947

- 136

https://twitter.com/PatrickMoorhead/status/950229121233137664

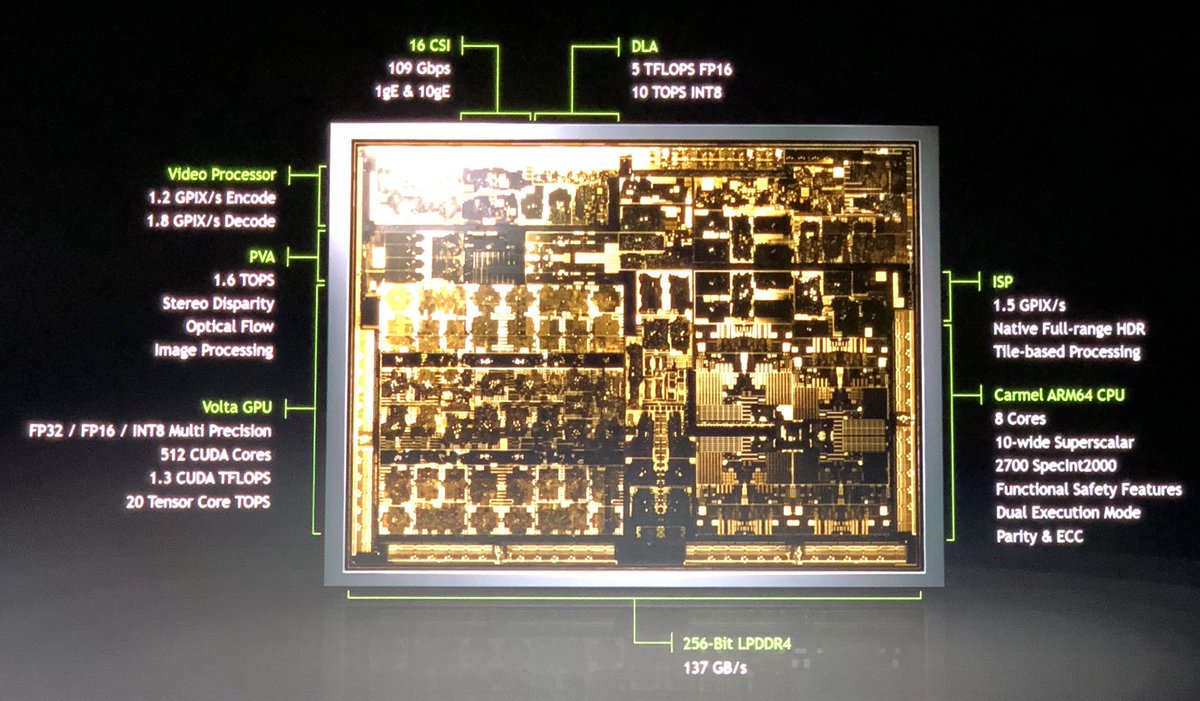

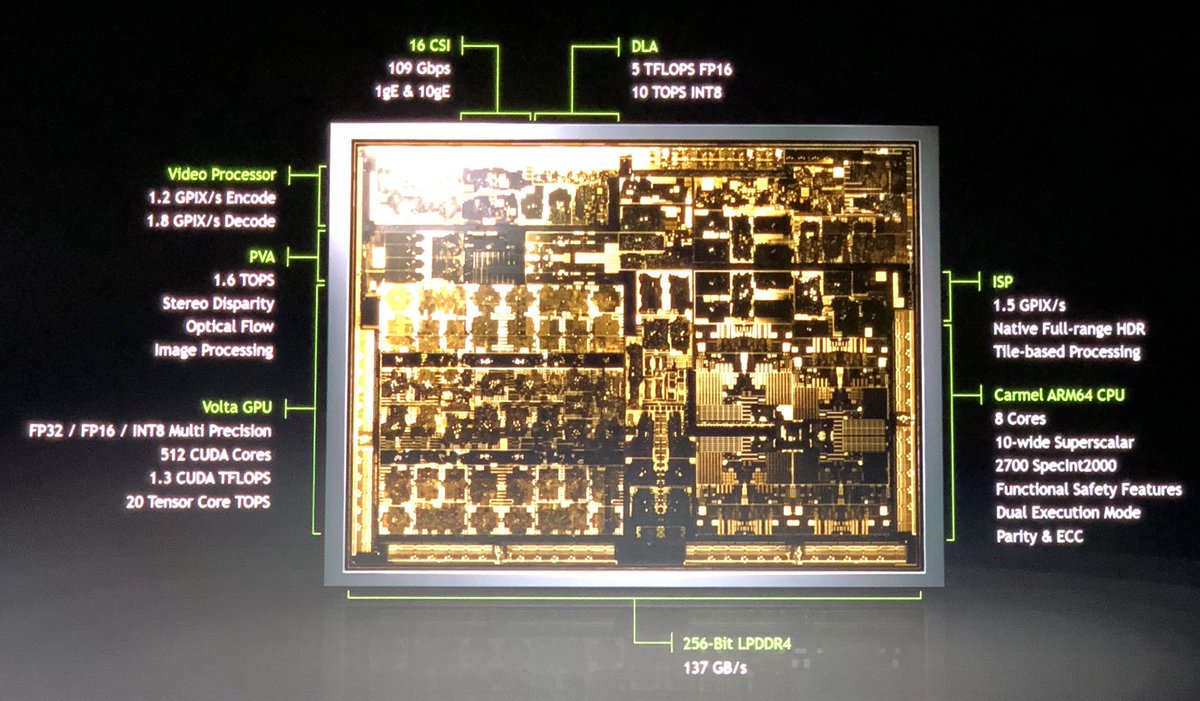

Announced at CES as part of their self-driving car SoC.

10 wide, even wider than Denver...

is it wider than skylake and zen?

So why nVIDIA doesn't dare to enter to the laptop market?

You mean except for the Tegra X1 used in the Nintendo Switch?Anyway, NVidia don't currently make any SoCs suitable for laptops or tablets. They used to make tablet SoCs, but all their latest ones are more focused on automotive.

You mean except for the Tegra X1 used in the Nintendo Switch?

But now they have a real promise with Parker and Xavier!They got burned once before with Windows RT, remember?

Anyway, NVidia don't currently make any SoCs suitable for laptops or tablets. They used to make tablet SoCs, but all their latest ones are more focused on automotive.

Do we know if this is another transmeta design like denver?

is it wider than skylake and zen?

I don't think you can compare them if Nvidia still uses the VLIW architecture with runtime JIT in software.Zen has a 6-wide front end, and 8-wide retire.

They used the same terminology "x-issue superscalar" for Denver, so I would say the architecture principle is the same, still Transmeta.

I don't think you can compare them if Nvidia still uses the VLIW architecture with runtime JIT in software.

The original Denver was also caleld "7-issue superscalar", and it wasn't a tremendously strong core.

Speaking of Denver: https://twitter.com/FioraAeterna/status/855445075341398017

And here we go again... Another bug?

10 wide, even wider than Denver...

Oh wow, that bug is fun!

Yeah, everything is multi-threaded.Phoronix have got their hands on one of these, and ran a few quick benchmarks:

https://www.phoronix.com/scan.php?page=article&item=nvidia-carmel-quick&num=1

I don't think any of their tests are single threaded, sadly, so tricky to tell how ST performance has scaled.

Something is telling to me that the Carmel board is not well configured...Yeah, everything is multi-threaded.

Someone posted the same benchmarks with a properly configures Jetson TX2 board: https://openbenchmarking.org/result/1809258-RA-1809248RA57. Read the comments: https://www.phoronix.com/forums/for...quick-test-of-nvidia-s-carmel-cpu-performance

It looks like Phoronix runs the TX2 in default mode where only 4 cores are being used (the Cortex-A57). When the SoC is set to run its 6 cores, then TX2 is faster than Xavier.

I hope soSomething is telling to me that the Carmel board is not well configured...

The Tegra X1 is the last one that was tablet suitable, and is pretty old now- it's a 20nm SoC in a 10nm world. They announced it three years ago!