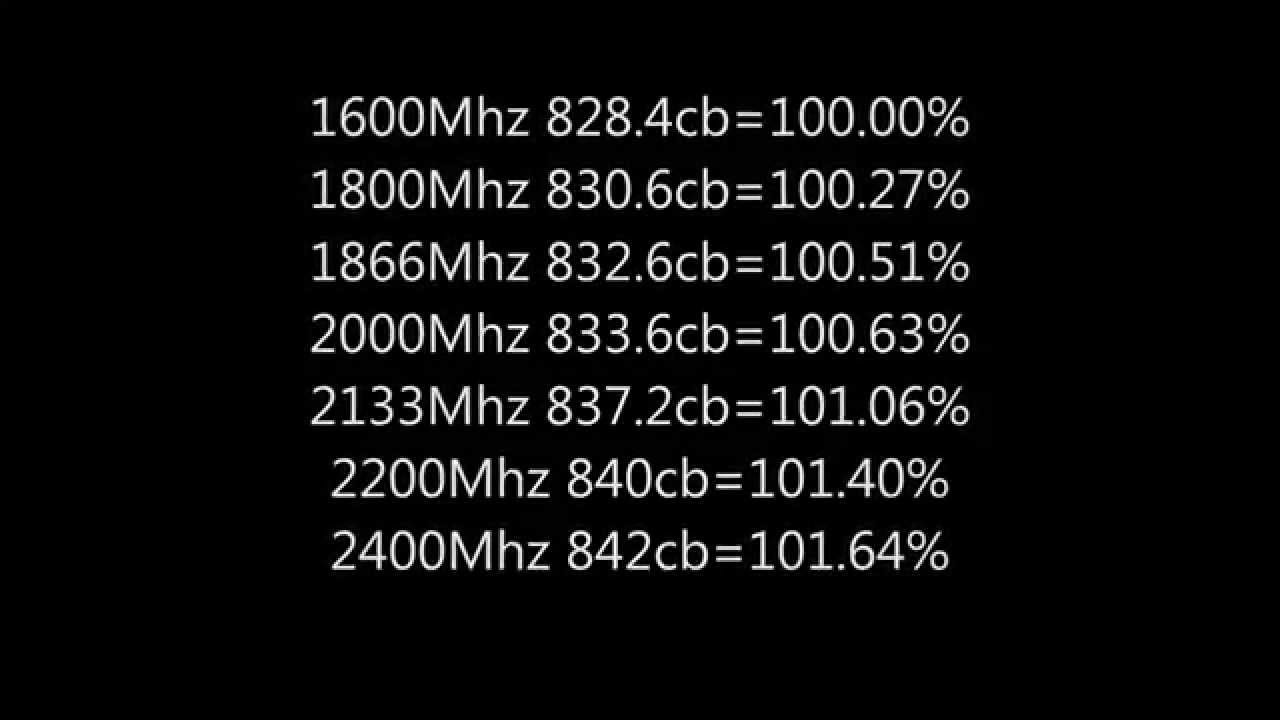

This is from a post in the thread. A few of us were discussing the chance of a 2 core leech OR 1 active memory controller / die instead of the normal 2. The Stilt did some quick memory test and got the results below, suggesting that rerouted traces in the package would be a superior solution. The whole of Pg4 of that thread has a lot of posts on the topic. Whether it happens or not, is another question.

https://forums.anandtech.com/thread...-top-tdp-of-250w.2547899/page-4#post-39451806

Post:

"Based on the quick synthetic tests the best option would be having 1CH per die, which of course would require active IMCs on each of the dies and totally reworked SP3r2 package (memory pad arrangement wise, which is very unlikely to happen).

1950X at fixed 3.4GHz frequency, 2933MHz MEMCLK CL14-14-14-1T.

3RA

2CPD (NUMA) = 85961MB/s (Read), 86643MB/s (Write), 81097MB/s (Copy), 78.33ns

1CPD (NUMA) = 44458MB/s (Read), 43449MB/s (Write), 40789MB/s (Copy), 78.80ns

2+0 CPD (LEECH) = 34495MB/s (Read), 37059MB/s (Write), 34823MB/s (Copy), 127.00ns"