Fjodor2001

Diamond Member

- Feb 6, 2010

- 4,592

- 739

- 126

Where does it say that? I'd assume it should be one 8P+16E die and 4 LP cores on IOD.28C lineup is using 2*(4+8) Dies

Where does it say that? I'd assume it should be one 8P+16E die and 4 LP cores on IOD.28C lineup is using 2*(4+8) Dies

There was some leaks regarding to it somewhere they had a choice to make 2*(4+8) or a single 8+16 it's up to Intel how they want to.Where does it say that? I'd assume it should be one 8P+16E die and 4 LP cores on IOD.

They can't mix and match within the same sku unless the L3 is entirely unified between the two chiplets (I doubt it will be).They have the flexibility to do many mix and match and what SKUs comes are not decided yet.

They can if they can mix Generation than mixing SKU is a piece of cakeThey can't mix and match within the same sku unless the L3 is entirely unified between the two chiplets (I doubt it will be).

Otherwise people will be mad figuring out the 4+8 x 2 sku with less L3 cache per CCD, than the 8+16 one lol.

Maybe a 8+16 i5 -k sku will be the N2 tile, and the non-k sku will be the 18A double tiles one, if the cost savings of going internal offsets any extra packaging cost.

How so? Do you think the L3 will be unified between tiles then, unlike what AMD does?They can if they can mix Generation than mixing SKU is a piece of cake

ADL and RPL part of same generation they can do anything tbh it's marketing in the endHow so? Do you think the L3 will be unified between tiles then, unlike what AMD does?

Well you wrote "28C lineup is using 2*(4+8) Dies" like it was certain it was going to use that. Never heard about that rumor, when was that leaked and do you have any link the source?There was some leaks regarding to it somewhere they had a choice to make 2*(4+8) or a single 8+16 it's up to Intel how they want to.

Internal volume anything can change NVL is the most flexible gen for them also fun fact looking at the arrangement it make total sense full die 8+16 half die 4+8 and than remove 8 E cores it becomes a 4+0 die clever design from Intel.Well you wrote "28C lineup is using 2*(4+8) Dies" like it was certain it was going to use that. Never heard about that rumor, when was that leaked and do you have any link the source?

Also, was there any reasoning why they would use "2*(4+8) Dies" only for the 28C, and 8P+16E dies for the rest of the SKUs (or binned variants of that with a few less cores)? Seems strange to have a dedicated 4P+8E die only for the 28C variant.

I'll wait until Zen 7 and the new socket. That generally gets me one CPU ONLY upgrade some time in the future. I am already at that position with my AM4 mb, so as long as the ole girl keeps on coming to the show every day, I'll be sticking with herI'll probably be upgrading my current Zen3 CPU+Motherboard+RAM system in 2026.

Disappointing that the bLLC or whatever it is called will be limited to an 8 P core die, without hyperthreading. Seems like they will already be at a disadvantage vs Zen 5 vCache which has 8 cores with HT, and at an even bigger disadvantage if Zen 6 goes to a 12 core CCD with vCache. Leave it to Intel to finally come up with a possible competitive architecture but have it be too little/too late and handicapped by the hybrid architecture and the decision to ditch HT.

So there was no source and you were just speculating. That's fine but it would be nice if you made that clear from the beginning.Internal volume anything can change NVL is the most flexible gen for them also fun fact looking at the arrangement it make total sense full die 8+16 half die 4+8 and than remove 8 E cores it becomes a 4+0 die clever design from Intel.

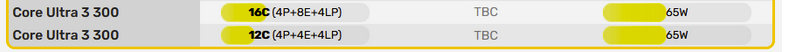

View attachment 127654

I am not speculating except for the last part about the fun fact the die config I am pretty sure I saw somewhere on Chinese forum can't remember exactly.So there was no source and you were just speculating. That's fine but it would be nice if you made that clear from the beginning.

You're forgetting the E-cores. It's NVL-S 8P+16E = 24C/24T vs 12C/24T Zen6 for the SKUs with bLLC / X3D.Disappointing that the bLLC or whatever it is called will be limited to an 8 P core die, without hyperthreading. Seems like they will already be at a disadvantage vs Zen 5 vCache which has 8 cores with HT, and at an even bigger disadvantage if Zen 6 goes to a 12 core CCD with vCache. Leave it to Intel to finally come up with a possible competitive architecture but have it be too little/too late and handicapped by the hybrid architecture and the decision to ditch HT.

Some random Chinese forum.... hehe... right... 🤔 I'm a bit skeptical about that until I've seen some more concrete evidence.I am not speculating except for the last part the die config I am pretty sure I saw somewhere on Chinese forum can't remember exactly.

Like I said 2*(4+8) is on 18AP and 8+16 is on N2 so internal vs external and for Chinese forums I waste too much of time there sometime so some things get fed Into my brain.Some random Chinese forum.... hehe... right... 🤔 I'm a bit skeptical about that until I've seen some more concrete evidence.

Anyway what would be the point of composing the 28C SKU from 2*(4P+8E) instead of 1*(8P+16E)?

(Plus 4LP cores for both alternatives.)

I can understand that Intel might want to do a 4P+8E = 12C SKU using half a 8P+16E die though, but that's another story.

You did not say "2*(4+8) is on 18AP and 8+16 is on N2" before , but I see now that Geddagod hinted at it.Like I said 2*(4+8) is on 18AP and 8+16 is on N2 so internal vs external and for Chinese forums I waste too much of time there sometime so some things get fed Into my brain.

I said it being internalYou did not say "2*(4+8) is on 18AP and 8+16 is on N2" before , but I see now that Geddagod hinted at it.

Anyway, I still do not understand why they would use 2*(4+8) on 18AP only for the 28C SKU. Is it e.g. because 18AP is expected to perform better than N2, but Intel cannot manufacture 18AP dies big enough to fit 8+16 with sufficient yield? And for the 28C they are aiming for peak ST performance (or "peak few cores" at least) assuming it's aimed at gamers with the bLLC?

If instead 18AP is expected to perform worse than N2, I'd make more sense to only use 4+8 dies on 18AP for the 4+8 and 4+4 SKUs, where the latter one would be binned.

I am talking about gaming. Have they been able to utilize the E cores yet for gaming? If the bLLC actually makes it to market, will the E cores be able to utilize the extra cache anyway, and would there be a latency penalty? My understanding is that the E cores are pretty much still useless for gaming.You're forgetting the E-cores. It's NVL-S 8P+16E = 24C/24T vs 12C/24T Zen6 for the SKUs with bLLC / X3D.

What there are background thread on few E cores it depends entirely on how the game is architectedI am talking about gaming. Have they been able to utilize the E cores yet for gaming? If the bLLC actually makes it to market, will the E cores be able to utilize the extra cache anyway, and would there be a latency penalty? My understanding is that the E cores are pretty much still useless for gaming.

Unless Intel can somehow get the E cores working for gaming, their "gaming" chip will effectively be 8 cores/8 threads. AMD's "gaming" chip, if the 12 core CCD materializes, will be 12 cores/24 threads. As much as I would like to see Intel meet or even exceed AMD for the gaming crown, I just cant see it happening, unless they pull some magic out of the hat with the P core architecture.

They just need pour enough resources to help game developers to use them. Example of them doing that below:Unless Intel can somehow get the E cores working for gaming

They don't have much resources in this tbh either they optimized their ITD for auto handling or work with individual developers(difficult resourcing) or simply do this in Unreal/Unity(best approach imo).They just need pour enough resources to help game developers to use them. Example of them doing that below: