I am finding it hard to see how people will utilize 52 cores. I keep thinking that all that die space could do so much more and for more people if it were used a different way.

While 2028 is still a few years away, it is STILL hard to imagine that so many cores will be useful in consumer electronics.

Going a bit further, how will you feed such a beast? I suppose you could move the desktop up to higher bandwidth memory than DDR8000 (perhaps RDIMMs at 16000MT?)... or move to a quad channel memory setup?

Still, it's an awful big cost in die size, MB layout, and RAM to cater to cinebench isn't it?

You really make it sound like this will be going into a lot of consumer electronics. It won't.

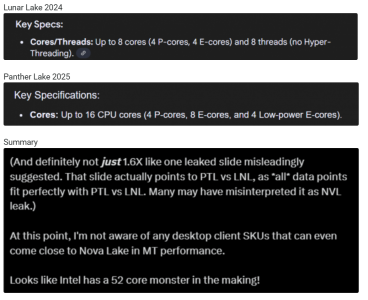

For starters, 52 cores is not going into most consumer electronics. It'll be the Ultra 9 CPU which is looking awfully similar to bringing the Extreme Edition line back (in specs and probably in price). According to the rumors, Intel is bringing back the Ultra 3 line for the bulk of consumer electronics (4P + 8E + 4LP-E) or (4P + 4E + 4LP-E). Amongst Meteor Lake, Lunar Lake, and Arrow Lake there was just one Ultra 3 CPU available.

It looks increasingly like Intel will have three main options: (1) Two CPU tiles for computational heavy CPUs, (2) one CPU tile + one cache tile for cache heavy tasks like gaming, and (3) just one CPU tile and probably a space filler tile for the rest of users. The die space IS doing so much more when users get to pick and choose the die space and how it is utilized.

Quad channel memory is the simplest way to feed it. Motherboard tracing will be much more complex, but that is a problem that is already solved. Note: I have no information that Intel is doing quad channel, but that would be the simplest way to address your concern.

It isn't a big cost in die size because only the few people who buy them will pay for it. And even though we act like die space is expensive, in a CPU that probably will sell in the $1000 range, one more tile is actually a small fraction of that cost. The RAM itself isn't any more expensive either. Just a more complex motherboard.

Finally, if you think Cinebench is the only reason for high-throughput computations, then you should probably go learn a few things about various consumer uses before posting.