-

We’re currently investigating an issue related to the forum theme and styling that is impacting page layout and visual formatting. The problem has been identified, and we are actively working on a resolution. There is no impact to user data or functionality, this is strictly a front-end display issue. We’ll post an update once the fix has been deployed. Thanks for your patience while we get this sorted.

You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

Discussion Intel current and future Lakes & Rapids thread

Page 363 - Seeking answers? Join the AnandTech community: where nearly half-a-million members share solutions and discuss the latest tech.

How many cores in one die?

56 cores for the whole SKU according to NBC.

First pictures leak of Intel's upcoming Sapphire Rapids Xeon CPUs, but 2022 release date could make it a tough sell in the face of Zen 4 EPYC Genoa

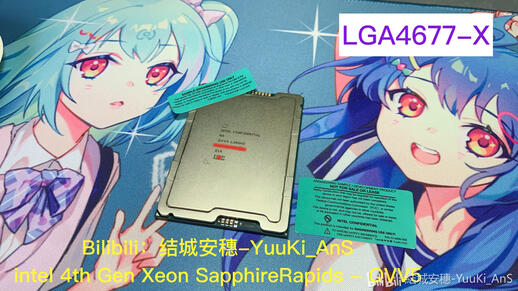

Chinese tipster @YuuKi_AnS released what appear to be the first leaked images of Intel's upcoming Sapphire Rapids Xeon server processor. Featuring up to 56 Golden Cove cores, Sapphire Rapids would be Intel's first server processor built on 10nm lithography.

www.notebookcheck.net

www.notebookcheck.net

HurleyBird

Platinum Member

56 is too few imho.

SAAA

Senior member

Rumor is 15 with one disabled for yield.How many cores in one die?

Anyone else hoping for HEDT of 418mm^2 of 10nm silicon?

That's a big piece of HEDT for 10 nm!

1672mm2 vs 1396mm2 for more cores (60vs56) and faster (+40% IPC?)… the die size is quite large but if this is Golden cove I can see it happening even with 10 nm process shrink.

56 is too few imho.

Thought so but then 4 x 56 is too much...

Rumor is 15 with one disabled for yield.

I suppose that could work if they keep the tile structure in the core. 15 cores plus one IMC one. 16 tiles does seem low for 418 mm2 but I wouldn't say it's wrong either.

Regarding the die size, keep in mind the die covering the top SKUs will feature a massive amount of next-gen IO - HBM2 & DDR5/DDR4 memory controllers and PCIe 5 with CXL 1.1 functionality. Also the amount of required additional "MCM glue logic" is unknown at this point.

The current-gen 4 Willow Cove client cores including L3 are around 43mm2 on the Intel Super 10nm. 16 of them should be over 170mm2. That's excluding the whole IO, probably larger L3 and Golden Cove size increases.

Looking at the XCC Cascade Lake, the "uncore" occupies roughly 40% of the die size. So 16 cores seems a bit low. 20 of them would take a bit over 210mm2. That would fit that 418mm2 chiplet a bit better.

The current-gen 4 Willow Cove client cores including L3 are around 43mm2 on the Intel Super 10nm. 16 of them should be over 170mm2. That's excluding the whole IO, probably larger L3 and Golden Cove size increases.

Looking at the XCC Cascade Lake, the "uncore" occupies roughly 40% of the die size. So 16 cores seems a bit low. 20 of them would take a bit over 210mm2. That would fit that 418mm2 chiplet a bit better.

uzzi38

Platinum Member

There's no DDR4 IMCs but otherwise yes. Most of the die area for each of these chiplets are going to be filled with I/O.Regarding the die size, keep in mind the die covering the top SKUs will feature a massive amount of next-gen IO - HBM2 & DDR5/DDR4 memory controllers and PCIe 5 with CXL 1.1 functionality. Also the amount of required additional "MCM glue logic" is unknown at this point.

The current-gen 4 Willow Cove client cores including L3 are around 43mm2 on the Intel Super 10nm. 16 of them should be over 170mm2. That's excluding the whole IO, probably larger L3 and Golden Cove size increases.

Looking at the XCC Cascade Lake, the "uncore" occupies roughly 40% of the die size. So 16 cores seems a bit low. 20 of them would take a bit over 210mm2. That would fit that 418mm2 chiplet a bit better.

Interested to see exactly how many cores are actually on each die though, because I don't think it's 15...

The current-gen 4 Willow Cove client cores including L3 are around 43mm2 on the Intel Super 10nm. 16 of them should be over 170mm2. That's excluding the whole IO, probably larger L3 and Golden Cove size increases.

Saphhire is using Golden Cove, and surely that is going to be a lot bigger than a Willow Cove Core. Plus the second AVX-512 unit, the mesh logic, the server exclusive features, any additional cache... Skylake Server's tile is close to 18 mm2 so only 15 cores and the one IMC tile is not crazy.

I suppose that Saphhire is going to end up being a HPC only product.

My bad, DDR4 is for ADL. The server platform makes sense to be DDR5 only.There's no DDR4 IMCs but otherwise yes. Most of the die area for each of these chiplets are going to be filled with I/O.

The HBM SKUs will surely be aimed towards HPC, although the conventional DDR ones might be fine for general purpose.

uzzi38

Platinum Member

I suppose that Saphhire is going to end up being a HPC only product.

Nah, it's not HPC only. The HBM2 ones might be for all I know, but SKUs that don't use HBM2 should be generally available at the very least on the high end of the market.

Gigabyte Technology Co., Ltd. Z490 AORUS MASTER - Geekbench

Benchmark results for a Gigabyte Technology Co., Ltd. Z490 AORUS MASTER with a 11th Gen Intel Core i9-11900K processor.

New GB5 score of what looks like a retail 11900K. 1894 is really good for ST.

Alder Lake is already DDR5.My bad, DDR4 is for ADL. The server platform makes sense to be DDR5 only.

The HBM SKUs will surely be aimed towards HPC, although the conventional DDR ones might be fine for general purpose.

Alder Lake is already DDR5.

Alder supports both and it sounds like DDR4 is going to be what most people use.

blckgrffn

Diamond Member

Gigabyte Technology Co., Ltd. Z490 AORUS MASTER - Geekbench

Benchmark results for a Gigabyte Technology Co., Ltd. Z490 AORUS MASTER with a 11th Gen Intel Core i9-11900K processor.browser.geekbench.com

New GB5 score of what looks like a retail 11900K. 1894 is really good for ST.

Yeah, that would be a pretty big increase. A 10900k scores ~1400.

Intel Core i9-10900K Benchmarks - Geekbench

That would be a 35% increase. That's... higher than my reasonable expectations, I guess. That would be sweet if true 🙂

Yeah, that would be a pretty big increase. A 10900k scores ~1400.

Intel Core i9-10900K Benchmarks - Geekbench

browser.geekbench.com

That would be a 35% increase. That's... higher than my reasonable expectations, I guess. That would be sweet if true 🙂

The AES score is part of that. Also forgot to mention that the Rocket Lake sample might be overclocked.

Actually it broken the 1900 barrier: https://browser.geekbench.com/v5/cpu/6348421

The AES score is a small part, the IPC at 5300 Mhz is higher than on Tigerlake-U 4700 Mhz. This RKL-S sample uses DDR4-3600 and tighter latencies. Tigerlake-U runs with DDR4-3200 CL22 or LPDDR4-4266 CL36 and this might have run with DDR4-3600 CL15. Bandwidth isn't really important for ST workloads unlike latencies.

The AES score is a small part, the IPC at 5300 Mhz is higher than on Tigerlake-U 4700 Mhz. This RKL-S sample uses DDR4-3600 and tighter latencies. Tigerlake-U runs with DDR4-3200 CL22 or LPDDR4-4266 CL36 and this might have run with DDR4-3600 CL15. Bandwidth isn't really important for ST workloads unlike latencies.

uzzi38

Platinum Member

Memory has little to no effect on GB5 at all. On my 5950X I saw no improvement in performance between JEDEC DDR4-2133 and DDR4-3200cl16.Actually it broken the 1900 barrier: https://browser.geekbench.com/v5/cpu/6348421

The AES score is a small part, the IPC at 5300 Mhz is higher than on Tigerlake-U 4700 Mhz. This RKL-S sample uses DDR4-3600 and tighter latencies. Tigerlake-U runs with DDR4-3200 CL22 or LPDDR4-4266 CL36 and this might have run with DDR4-3600 CL15. Bandwidth isn't really important for ST workloads unlike latencies.

Det0x

Golden Member

Gigabyte Technology Co., Ltd. Z490 AORUS MASTER - Geekbench

Benchmark results for a Gigabyte Technology Co., Ltd. Z490 AORUS MASTER with a 11th Gen Intel Core i9-11900K processor.browser.geekbench.com

New GB5 score of what looks like a retail 11900K. 1894 is really good for ST.

Seems pretty good

Rocket lake seems to be getting alot of its score from AES.

Comparison with my Zen3 here: https://browser.geekbench.com/v5/cpu/compare/6348081?baseline=6050938

Last edited:

Memory has little to no effect on GB5 at all. On my 5950X I saw no improvement in performance between JEDEC DDR4-2133 and DDR4-3200cl16.

It has quite a big effect on the AES score and unless Cypress Cove has a bigger IPC than Willow or Sunny Cove it seems to have an effect on RKL-S as well.

SAAA

Senior member

So by the end of this year or next one we'll have stock CPUs pushing 2000+ points. From both vendors probably.

Looking good, in spite of x86 decadence and limitations talks.

Sure power is another matter (we'll see how big little on desktop helps with that) but when it comes to max performance they aren't stopping.

I also keep hearing the 72 number for Sapphire. Maybe it's indeed 18 cores each tile and several disabled for yield, or there's two variants with different layouts...

If they can peek inside that naked chip we'll have a quick answer.

18 each tile would also work nicely as HEDT successor to the aged i9-10980XE. Same core count but huge generation gains and platform changes.

Looking good, in spite of x86 decadence and limitations talks.

Sure power is another matter (we'll see how big little on desktop helps with that) but when it comes to max performance they aren't stopping.

I suppose that could work if they keep the tile structure in the core. 15 cores plus one IMC one. 16 tiles does seem low for 418 mm2 but I wouldn't say it's wrong either.

I also keep hearing the 72 number for Sapphire. Maybe it's indeed 18 cores each tile and several disabled for yield, or there's two variants with different layouts...

If they can peek inside that naked chip we'll have a quick answer.

18 each tile would also work nicely as HEDT successor to the aged i9-10980XE. Same core count but huge generation gains and platform changes.

TRENDING THREADS

-

Discussion Zen 5 Speculation (EPYC Turin and Strix Point/Granite Ridge - Ryzen 9000)

- Started by DisEnchantment

- Replies: 25K

-

Discussion Intel Meteor, Arrow, Lunar & Panther Lakes + WCL Discussion Threads

- Started by Tigerick

- Replies: 24K

-

Discussion Intel current and future Lakes & Rapids thread

- Started by TheF34RChannel

- Replies: 24K

-

-