SiliconFly

Golden Member

.

Last edited:

It all depends on how much of an IPC increase LionCove achieves and how it compares to Zen 5. LionCove is supposed to be enough for 2 generations of LGA1851 processors and for the next generation of Xeon processors.Agreed. But how can Diamond Rapids be the "big breakthrough" then? It has the exact same problem that you pointed out for GNR. LNC cores are okay against Turin. But they will NOT be okay against Venice. So in my opinion Diamond Rapids is dead already if it has LNC cores.

Even witeken tends to talk too much about GNR!

But honestly, GNR is based on RWC (not LNC). So, it's gonna inherit all the power hungry issues that SPR & EMR had. Intel's will have it's big break with Diamond Rapids (with LNC) and not before imho. I'm not a big fan of server parts and don't read too much into them, but from what I gather, GNR may just DOA (like SPR & EMR) cos in servers TDP matters a lot. Don't understand why some believe it's going to be a great product.

Plenty, part still has horrible PPA even in its MCC incarnation (34c at 700mm^2 die is nasty).How much of Sapphire Rapids' problems stem from the cores rather than the packaging/interconnect?

Didn't Emerald Rapids partially solve that problem? The performance wasn't stellar but perf/watt was improved. It was just too late and was never going to be competitive with Genoa.Plenty, part still has horrible PPA even in its MCC incarnation (34c at 700mm^2 die is nasty).

No, but it did DTCO the living hell out of LLC.Didn't Emerald Rapids partially solve that problem?

It better do. but again, I'm talking MCC, which is ~unchanged for EMR.but perf/watt was improved

yeah not news, TACC posted SPR-HBM findings awhile ago.

Intel's HBM ploy didn't work out either. I think they really have a culture of "let's brute force this first and think later!".

12 (twelve) days!May exceed Venice too.

It was bad. real bad.

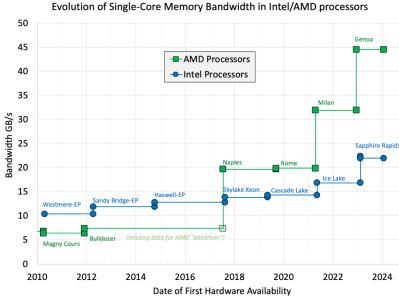

The issue is their mesh and uncore being all sorts of woeful.The evolution of single-core bandwidth in multicore systems — update

sites.utexas.edu

View attachment 99380

I keep telling Intel, go back to using eDRAM!!!

It's probably better than whatever crap they have going on currently in their server CPUs.

Recently, someone on reddit by the username of mooreslawisnotdead posted an Intel roadmap all the way through 2025. This roadmap contains some products/code names that haven't been mentioned here before. The roadmap could be completely genuine or a total work of fan fiction. I guess that's for you to decide. The user has since deleted his account, but not before I copied this information. What follows is the roadmap itself, along with commentary by the reddit user that posted it:

---------------------------------------------------------------------------------------------

Alder Lake (Golden Cove/Gracemont) Q4'21 / Q1'22 - predicted to be competitively weak vs AMD/Apple offerings that time.

Raptor Lake (Raptor Cove / Gracemont) Q3'22 / Q4'22 - 10% CPU perf boost and 8/16 configuration puts intel back on par but expect AMD/Apple to refresh their products as well.

Meteor Lake (Redwood Cove / Crestmont) Q2'23 - Intel's first true chiplet or tile based design. Different dies built on TSMC / Intel processes. More of a node shrink with single digit performance improvements. AMD will again extend lead with Zen 4+ / 5.

Arrow Lake (Lion Cove / Skymont) Q4'23 - Will feature an updated compute tile with 8/32 config for the high end enthusiast products. Might achieve parity with AMD offerings at the time but loses out to Apple in power efficiency.

Lunar Lake (Lion Cove / Skymont) Q4'24 - This is the product that will use TSMC 3nm as reported by Nikkei. Big performance jump expected and designed to achieve parity or beat AMD and Apple in both performance and power efficiency.

Nova Lake (Panther Cove [tentative]/ Darkmont) 2025 - This will mark the biggest architectural change in cpu architecture since the Core architecture is introduced in 2006. Intel is working to build an entirely new architecture from the ground up much like Ryzen with up to 50% cpu performance improvement from lunar lake. This is also the reason why Glenn Hinton returned.

---------------------------------------------------------------------------------------------

Almost 3 years ago we had this leak. Looks like Arrow Lake was delayed (so Raptor Lake Refresh). But removing the delays Intel is following this leak.

Even witeken tends to talk too much about GNR!

But honestly, GNR is based on RWC (not LNC).

The RWC in Granite Rapids is not exactly the same core as the one in client, but an enhanced one with improved branch prediction and memory parallelism capabilities.How much of Sapphire Rapids' problems stem from the cores rather than the packaging/interconnect? Emerald Rapids was a decent (if belated) step forward. No, I don't think Granite Rapids will be good competition Turin at all. But as a successor to Sapphire and Emerald Rapids, it should be quite a step forward, at least in terms of efficiency.

APUs are fine for it. DT Copilot + PC is a niche market and will be driven more by OEMs pushing it rather than actual demand.I don't know what AMD plans to do about Zen 5 not having an NPU. Maybe they will release Zen 5 APUs to fulfill that need? But then, it won't be a direct competitor to Arrow Lake K series since the APUs don't approach the performance of X series AMD CPUs.

I don't think LNC has the same problem RWC has. LNC is expected to be an efficient architecture. Also, Diamond Rapids is based on LNC+ (second iteration of LNC). Should bring in more performance/efficiency over existing LNC designs. May exceed Venice too.

The RWC in Granite Rapids is not exactly the same core as the one in client, but an enhanced one with improved branch prediction and memory parallelism capabilities.

Pat said 10-plus percent. This is just like the E cores where Sierra Glen has no changes uarch wise but Crestmont does. Another indicator is that the 80-core version has 40% improved performance at the same TDP level(thus 40% improved perf/W) over 64 core Emerald Rapids, so a lot of that gain is coming from other than clocks.

Also it'll be much more competitive than it is today, where Emerald Rapids slots firmly in the mid in terms of pricing.

5th Gen Intel Xeon Processors Emerald Rapids Resets Servers by Intel

We delve into the 5th Gen Intel Xeon Scalable Emerald Rapids generation and talk both the performance and platform gains around the new chipswww.servethehome.com

That's because Meteorlake's P core only has doubled L1I cache as an improvement.RedwoodCove in Xeon looks exactly the same as in MeteorLake. Intel just isn't bragging about the IPC improvements in Meteorlake because the first attempt at tiles killed the IPC growth. However, RedwoodCove in Xeon will benefit from an increase in IPC.

I know that. It seems strange that there would be two different architectures between GoldenCove and LionCove? I know these are unsubstantiated claims on my part, but I believe it's the same core. High resolution shots and comparison with MeteorLake should dispel doubts.That's because Meteorlake's P core only has doubled L1I cache as an improvement.

P cores:

Meteorlake-

Granite Rapids:

On P cores it says "Improved performance efficiency" with zero mention of architectural additions on Meteorlake, while on Granite Rapids it says: "Improved Branch predictor and miss recovery, 3-cycle FP multiplication, More outstanding memory requests and prefetch capabilities". Those are actually significant changes.

E cores:

Meteorlake-

Sierra Forest-

E cores on Meteorlake gets the 6-wide allocate/rename while on Sierra Forest it remains at 5, same as Gracemont. It also specifically says "IPC gains" and "Enhanced branch predicton" on Crestmont, not on Sierra Glen.

In both cases of Sierra Glen and Meteorlake's P core "improved performance efficiency" or "improved efficiency" means in terms of perf/clock they got nothing to show for. It's an excuse to add another bullet point.

Stop parroting what most others believe and actually look for yourselves people. They tell you right there. They aren't recycling cores this generation.

It's under a different code-name because it's on a different process, even if only has a minor architectural change. Pat has said it's like a + for Granite Rapids. Penryn, Ivy Bridge, Broadwell, all had minimal changes, but different code names because it's on a new process.Overall it's weird that in MeteorLake they only add 64KB L1-I and call it RedwoodCove. So there is a different core architecture in Xeon and it is not RedwoodCove because in Xeon it would be completely different than RedwoodCove. Or it's the same thing, but it's definitely not RedwoodCove+.

It would be an even bigger disappointment if it turned out that ArrowLake does not use LionCove, but the P Core architecture from GraniteRapids.

Die shots do not tell you everything, because Intel can choose to have it disabled. The Xeon differs in one aspect, which is having the 512-bit AVX512 unit, which the client does not have.High resolution shots and comparison with MeteorLake should dispel doubts.

If GraniteRapids has these changes and MeteorLake does not have them in P cores, then it is definitely not RedwoodCove+. And if the P cores have features enabled in GraniteRapids and disabled in Meteorlake, they are physically the same cores.It's under a different code-name because it's on a different process, even if only has a minor architectural change. Pat has said it's like a + for Granite Rapids. Penryn, Ivy Bridge, Broadwell, all had minimal changes, but different code names because it's on a new process.

RWC on Granite Rapids is obviously not Lion Cove, because it's not wide as Lion Cove is. But this makes sense and it fits with Pat's statement that the move to Intel 3 and a year delay allowed it to have additional changes.

Ultimately the names are not important and tells you little. They called it Goldmont Plus, but a significant gain of 30% per clock.

Die shots do not tell you everything, because Intel can choose to have it disabled. The Xeon differs in one aspect, which is having the 512-bit AVX512 unit, which the client does not have.

Everything older than Pentium Pro, the patents have expired. For everything else (AVX implementation, power management, virtualization, etc.) patents have not expired.