-

We’re currently investigating an issue related to the forum theme and styling that is impacting page layout and visual formatting. The problem has been identified, and we are actively working on a resolution. There is no impact to user data or functionality, this is strictly a front-end display issue. We’ll post an update once the fix has been deployed. Thanks for your patience while we get this sorted.

You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

Discussion Intel current and future Lakes & Rapids thread

Page 889 - Seeking answers? Join the AnandTech community: where nearly half-a-million members share solutions and discuss the latest tech.

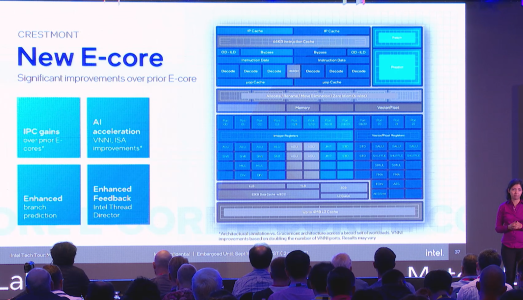

Gracemont has impressive ipc for a small core.. crestmont has 8% plus ipc.. Sierra forrest and clearwater should dominate with ease😏🏅💻

Let's wait and see how well it hangs onto clocks when all cores are loaded.

Base frequency on Bergamo is 2.25ghz. I don’t think that’s an impossible bar for SRF-AP.Let's wait and see how well it hangs onto clocks when all cores are loaded.

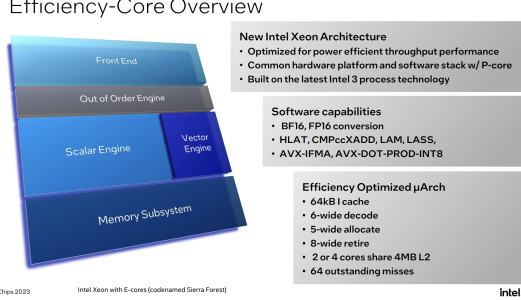

That must have been someone misspeaking the number 5 instead of 6. Every major site that covered Sierra Glen at Hot Chips says it is Crestmont and not Gracemont. Intel even shared many slides listing the new Sierra Glen E-core features at Hot Chips. https://www.intel.com/content/www/u...-forest-xeon-press-briefing-presentation.html

It's on a slide: 5 wide allocate for SRG E-core. Crestmont moves up to 6 wide there. SRG looks like a ported Gracemont with minor changes rather than ported Crestmont

It's on a slide: 5 wide allocate for SRG E-core. Crestmont moves up to 6 wide there. SRG looks like a ported Gracemont with minor changes rather than ported CrestmontGenuinely curious, how many server workloads do you think is going to be very INT heavy, scale up to hundreds of cores, and not care about L2?Base frequency on Bergamo is 2.25ghz. I don’t think that’s an impossible bar for SRF-AP.

No clue.Genuinely curious, how many server workloads do you think is going to be very INT heavy, scale up to hundreds of cores, and not care about L2?

SRF doesn’t really excite me if I’m being honest. However, even workloads that aren’t perfectly aligned with its strengths it should have enough raw compute power to brute force it. It’s going to have a pretty big bandwidth advantage to offset some of its weaknesses in those heavily parallel tasks too.

much more interested in GNR-AP personally.

gdansk

Diamond Member

These are for cloud server farms. Virtual machines and unimportant cores for customers using those X-as-a-Service products cloud vendors have. Very INT heavy. Doesn't need a workload to scale to hundreds of threads because they'll be sold as 2-8 vCPU bundles. And even with the lack of L2 they'll still be generally above Skylake which is the current expected performance.Genuinely curious, how many server workloads do you think is going to be very INT heavy, scale up to hundreds of cores, and not care about L2?

It's a very good fit, on paper, for the target market.

Why does core count per chip matter for that then? Other than cost savings for core per socket (which could be offset by higher interconnect power draw cost).These are for cloud farms. Ghetto cores for customers web services probably. Very INT heavy. Doesn't need a workload to scale to hundreds of threads because they'll be sold as 2-8 vCPU bundles. And the lack of L2 they'll still be generally above Skylake.

It's a very good fit, on paper, for the target market.

And also, why even use mesh acting like a monolithic L3 then?

gdansk

Diamond Member

When you only care about delivering a certain level of performance what is cheaper 1 288 core CPU drawing 400W+ or 240 threads from 2 x 60 Sapphire Rapids drawing 350W each? And a single socket motherboard is cheaper too.Why does core count per chip matter for that then? Other than cost savings for core per socket (which could be offset by higher interconnect power draw cost).

And also, why even use mesh acting like a monolithic L3 then?

As for the L3, I'm not sure. It's probably a simple way to allow communication between core clusters.

I have a nice little PC in my living room powered by an N100 (4 Gracemont cores, so skylake IPC) and it consumes, full load, less that 21W.Gracemont has impressive ipc for a small core.. crestmont has 8% plus ipc.. Sierra forrest and clearwater should dominate with ease😏🏅💻

An N200, on Intel4, using Crestmont + MTL iGPU would be the ultimate living room media/streaming PC.

dullard

Elite Member

Um, Crestmont is ported Gracemont with minor changes.It's on a slide: 5 wide allocate for SRG E-core. Crestmont moves up to 6 wide there. SRG looks like a ported Gracemont with minor changes rather than ported Crestmont

Right there on the slide you just posted shows the most obvious change to prove it isn't Gracemont. "2 or 4 cores share 4MB L2". No more are the chips limited to blocks of 4 E-cores. Instead, blocks of 2 E-cores can be used.

Other things to look for on that slide: "new", "optimized", and all those capabilities that aren't in Gracemont. Those capabilities include items such as AVX-IFMA (2x256-bit instructions so most but not all of AVX-512 can now be used), and new instructions such as cmpccxadd (compare then add if true: avoiding doing this task in two separate instructions and avoids having branches if the condition is not true).

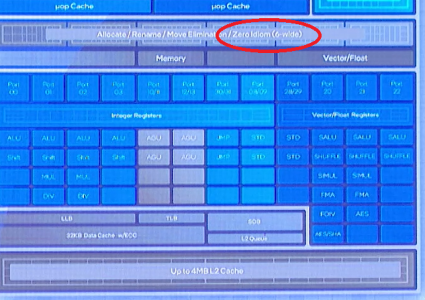

Instead it seems like you think there are no changes simply since one slide says 5-wide allocate (Sierra Forest at Hot Chips) and another slide says 6-wide Zero Idiom (Crestmont at Intel Innovation 2023)?

Last edited:

Ah that's my bad. I guess I misremembered the exact range of values.

They said it here at minute 22:45, the video can be downloaded: https://www.intel.com/content/www/u...ciency-replay.html?wapkw=Meteor Lake Tech Day

nicalandia

Diamond Member

Don't be disingenuous, you know what I mean...Um, Crestmont is ported Gracemont with minor changes.

Didn't I just say, gracemont with little changes? SRG appears to be based on gracemont, not that it quite literally is just gracemont.Right there on the slide you just posted shows the most obvious change to prove it isn't Gracemont.

Again, yes there are changes, but it doesn't appear to be Crestmont based. SRF has a completely different name for its small cores- Sierra Glenn.Other things to look for on that slide: "new", "optimized", and all those capabilities that aren't in Gracemont. Those capabilities include items such as AVX-IFMA (2x256-bit instructions so most but not all of AVX-512 can now be used), and new instructions such as cmpccxadd (compare then add if true: avoiding doing this task in two separate instructions and avoids having branches if the condition is not true).

Yes, when one slide shows changes in the architecture of a core, I will call them different cores lol. Moving from 5 wide to 6 wide rename is a pretty major change, in isolation. Crestmont is 6 wide rename as shown in this ssInstead it seems like you think there are no changes simply since one slide says 5-wide allocate (Sierra Forest at Hot Chips) and another slide says 6-wide Zero Idiom (Crestmont at Intel Innovation 2023)?

Yuuki Ans Delivering the Goods

View attachment 86075

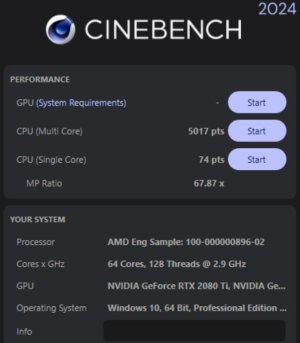

As reference: ES Sample Genoa

View attachment 86076

Whoever thinks Bergamo will strugle to dominate Sierra Forest is beign too optimistic. Those little cores have Ice Lake IPC at best and no SMT. Look how those fare against Genoa in SPEC 2017

I don't think there was ever much contention that Genoa would outperform SPR & EMR.

Interesting that from the CPU-Z screenshot EMR outperforms SPR 8490H 1T perf by ~20%, while underperforming nT perf by 25%. Fairly certain this ES sample doesn't represent final products nT performance. Overall EMR 1T performance looks pretty good.

dullard

Elite Member

I appreciate the effort, but you just posted the exact slide that I mentionedDon't be disingenuous, you know what I mean...

Didn't I just say, gracemont with little changes? SRG appears to be based on gracemont, not that it quite literally is just gracemont.

Again, yes there are changes, but it doesn't appear to be Crestmont based. SRF has a completely different name for its small cores- Sierra Glenn.

Yes, when one slide shows changes in the architecture of a core, I will call them different cores lol. Moving from 5 wide to 6 wide rename is a pretty major change, in isolation. Crestmont is 6 wide rename as shown in this ss

I don't see what you gain (or how it helps move this conversation forward) by posting an image for me that I quoted.Instead it seems like you think there are no changes simply since one slide says 5-wide allocate (Sierra Forest at Hot Chips) and another slide says 6-wide Zero Idiom (Crestmont at Intel Innovation 2023)?

Again, don't get mixed up by a typo. Sierra Glen is a ported Crestmont, not ported Gracemont. Not much difference between Crestmont and Gracemont, but Sierra Forest has Crestmont features.

Last edited:

They use the exact same terminology was my point. They said crestmont was 6 wide allocate as well, and claimed SRG was 5 wide allocate.I don't see what you gain by posting an image for me that I quoted.

I don't think it's a typo...Again, don't get mixed up by a typo.

Doesn't look like it....Sierra Glen is a ported Crestmont, not ported Gracemont.

What seems to be the biggest difference for Crestmont vs Gracemont, and prob the biggest reason for the IPC gains, is moving to a wider allocate stage... and Sierra Glenn apparently doesn't have that.Not much difference between Crestmont and Gracemont, but Sierra Forest has Crestmont features.

What other "crestmont features" does Sierra Glenn have (that gracemont doesn't)?

What do You mean? They have more L2 than P cores. Sure it is shared by 2 or 4 cores, but in their intended use, it is plenty and keeps L2 misses and fabric traffic low. It reduces MT when all cores are lit, but helps with perf otherwise.. And even with the lack of L2 they'll still be generally above Skylake which is the current expected performance.

EMR is looking great. Memory is looking much tighter, cache is 300MB and ~5ns less latency than SPR. Good job Intel!

Last edited:

dullard

Elite Member

Try reading here: https://forums.anandtech.com/thread...ure-lakes-rapids-thread.2509080/post-41077534What other "crestmont features" does Sierra Glenn have (that gracemont doesn't)?

If you read that, you might notice a list of Crestmont features in Sierra Glen that Gracemont doesn't have (as in all of the changes between Crestmont and Gracemont).

Also claiming that Sierra Forest is based on Crestmont:

- Ryan Smith (Anandtech): https://www.anandtech.com/show/2003...etails-granite-rapids-and-sierra-forest-xeons

- Anton Shilov (Tom's Hardware): https://www.tomshardware.com/news/intel-grand-ridge-and-sierra-forest-cpus-gets-more-detailed

- Tech Power UP: https://www.techpowerup.com/313820/...rra-forest-out-to-eat-amd-epyc-bergamos-lunch

- Hardware Times: https://www.hardwaretimes.com/intel...o-tackle-amds-128-core-bergamo-and-arm-chips/

- Phoronix: https://www.phoronix.com/news/Linux-6.6-Perf-Events

- Wikichip: https://en.wikichip.org/wiki/intel/microarchitectures/sierra_forest

- Overclocking.com: https://en.overclocking.com/intel-sierra-forest-144-cores-and-108-mb-cache/

- Wccftech (yeah I went there): https://wccftech.com/intel-xeon-cpu...p-up-to-132-granite-rapids-ws-up-to-86-cores/

Last edited:

gdansk

Diamond Member

It depends on the configuration and I was speaking about Sierra Forest which is all E cores. I assume this stays with 4MB L2 shared by 4 core cluster for density. P core designs are at 2MB per core now, right? So about 2x the L2 per core. And I'm not complaining. If the cloud vendors keep a given customer within the same core cluster it will be good.What do You mean? They have more L2 than P cores. Sure it is shared by 2 or 4 cores, but in their intended use, it is plenty and keeps L2 misses and fabric traffic low. It reduces MT when all cores are lit, but helps with perf otherwise.

Last edited:

It depends on the configuration and I was speaking about Sierra Forest which is all E cores. I assume this stays with 4MB L2 shared by 4 core cluster for density. P core designs are at 2MB per core now, right? So about 2x the L2 per core. And I'm not complaining. If the cloud vendors keep customers within the same core cluster it will be good.

Yeah, but in such sea of cores having 4MB of L2 if just one thread is busy is better than 4x1MB caches. Sharing reduces nT but sT and overall SoC benefits.

Again, just because Sierra Glenn has features Gracemont does not, doesn't mean it's not based on Gracemont. Even in my original arguement, I said Sierra Glenn was slightly changed from Gracemont.Other things to look for on that slide: "new", "optimized", and all those capabilities that aren't in Gracemont. Those capabilities include items such as AVX-IFMA (2x256-bit instructions so most but not all of AVX-512 can now be used), and new instructions such as cmpccxadd (compare then add if true: avoiding doing this task in two separate instructions and avoids having branches if the condition is not true).

Compelling evidence for it being based on Crestmont would Sierra Glenn to have the features of Cresmont, and then some. It appears as if Sierra Glenn has the features of Gracemont (same core architecture) and then supports additional instructions with some tweaks in the core.

BTW, I don't even think Crestmont can support AVX-512. If it did, they would easily be able to claim MTL supports AVX10.

dullard

Elite Member

What you describe is exactly what Crestmont is.if Sierra Glenn has the features of Gracemont (same core architecture) and then supports additional instructions with some tweaks in the core.

You are correct there, Crestmont does not have AVX-512. I posted that is has some additional 2x256 features that can mimic part but not all of AVX-512.BTW, I don't even think Crestmont can support AVX-512. If it did, they would easily be able to claim MTL supports AVX10.

Saw that edit. I've had lost all respect for tech journos a long time ago lmao. Just starting from the top of the list for example, Anandtech recently put out an article on LNL claiming it's likely they they backported it to 20A. Don't know if it's the same author as your article though.Try reading here: https://forums.anandtech.com/thread...ure-lakes-rapids-thread.2509080/post-41077534

If you read that, you might notice a list of Crestmont features in Sierra Glen that Gracemont doesn't have (as in all of the changes between Crestmont and Gracemont).

Also claiming that Sierra Forest is based on Crestmont:

- Ryan Smith (Anandtech): https://www.anandtech.com/show/2003...etails-granite-rapids-and-sierra-forest-xeons

- Anton Shilov (Tom's Hardware): https://www.tomshardware.com/news/intel-grand-ridge-and-sierra-forest-cpus-gets-more-detailed

- Tech Power UP: https://www.techpowerup.com/313820/...rra-forest-out-to-eat-amd-epyc-bergamos-lunch

- Hardware Times: https://www.hardwaretimes.com/intel...o-tackle-amds-128-core-bergamo-and-arm-chips/

- Phoronix: https://www.phoronix.com/news/Linux-6.6-Perf-Events

- Wikichip: https://en.wikichip.org/wiki/intel/microarchitectures/sierra_forest

- Overclocking.com: https://en.overclocking.com/intel-sierra-forest-144-cores-and-108-mb-cache/

- Wccftech (yeah I went there): https://wccftech.com/intel-xeon-cpu...p-up-to-132-granite-rapids-ws-up-to-86-cores/

Crestmont is tweaked Gracemont in different ways than how they tweaked Sierra Glenn. If this was a diagram, we would start off with Gracemont, and then branch of too Crestmont, with a different branch that originates from Gracemont branching into Sierra Glenn. If it was Crestmont based, the diagram would be a straight line of Gracemont > Crestmont > Sierra Glenn (it's not this). The first option is correct, as Sierra Glenn has the 5 wide allocate stage of Gracemont, but if it was based off of Crestmont, it should have the upgraded 6 wide allocate.What you describe is exactly what Crestmont is.

TRENDING THREADS

-

Discussion Zen 5 Speculation (EPYC Turin and Strix Point/Granite Ridge - Ryzen 9000)

- Started by DisEnchantment

- Replies: 25K

-

Discussion Intel Meteor, Arrow, Lunar & Panther Lakes + WCL Discussion Threads

- Started by Tigerick

- Replies: 25K

-

Discussion Intel current and future Lakes & Rapids thread

- Started by TheF34RChannel

- Replies: 24K

-

-