Thunder 57

Diamond Member

Pat is ready 😁🏅💻

I'm sure you are too.

Pat is ready 😁🏅💻

Well, as of now there is no way to avoid context-switching completely. But we can mitigate the effects of context switching by setting process affinity & core pinning.I think that is where we differ. When there are plentiful E cores, there would be no need to preempt the preferred cores. We could finally have dedicated cores to our important programs with no* context switching, no preemption, etc. of those important tasks.

* Yes, gdansk, there would still be context switching of the unimportant tasks on unimportant cores.

"Usually" is not sufficient in my experience. I see all kinds of stutters and delays when background tasks kick in. Maybe it is fine with your tasks. But certainly not for me.

But we can mitigate the effects of context switching by setting process affinity & core pinning.

Ah, I remember the time when Intel was a serious brand.Pat is ready 😁🏅💻

I’ll catch the rerun and read the spoilers online.Pat is ready 😁🏅💻

Don't know why you hating, I love goofy ahh Intel lolAh, I remember the time when Intel was a serious brand.

same and also different generation different type of customers lol it's gonna be the funniest thing ever to some peopleDon't know why you hating, I love goofy ahh Intel lol

I don't hate them, but I facepalm. Intel has fallen quite low, and these foolish things they do with push-ups to raise people's interest confirm their status.Don't know why you hating, I love goofy ahh Intel lol

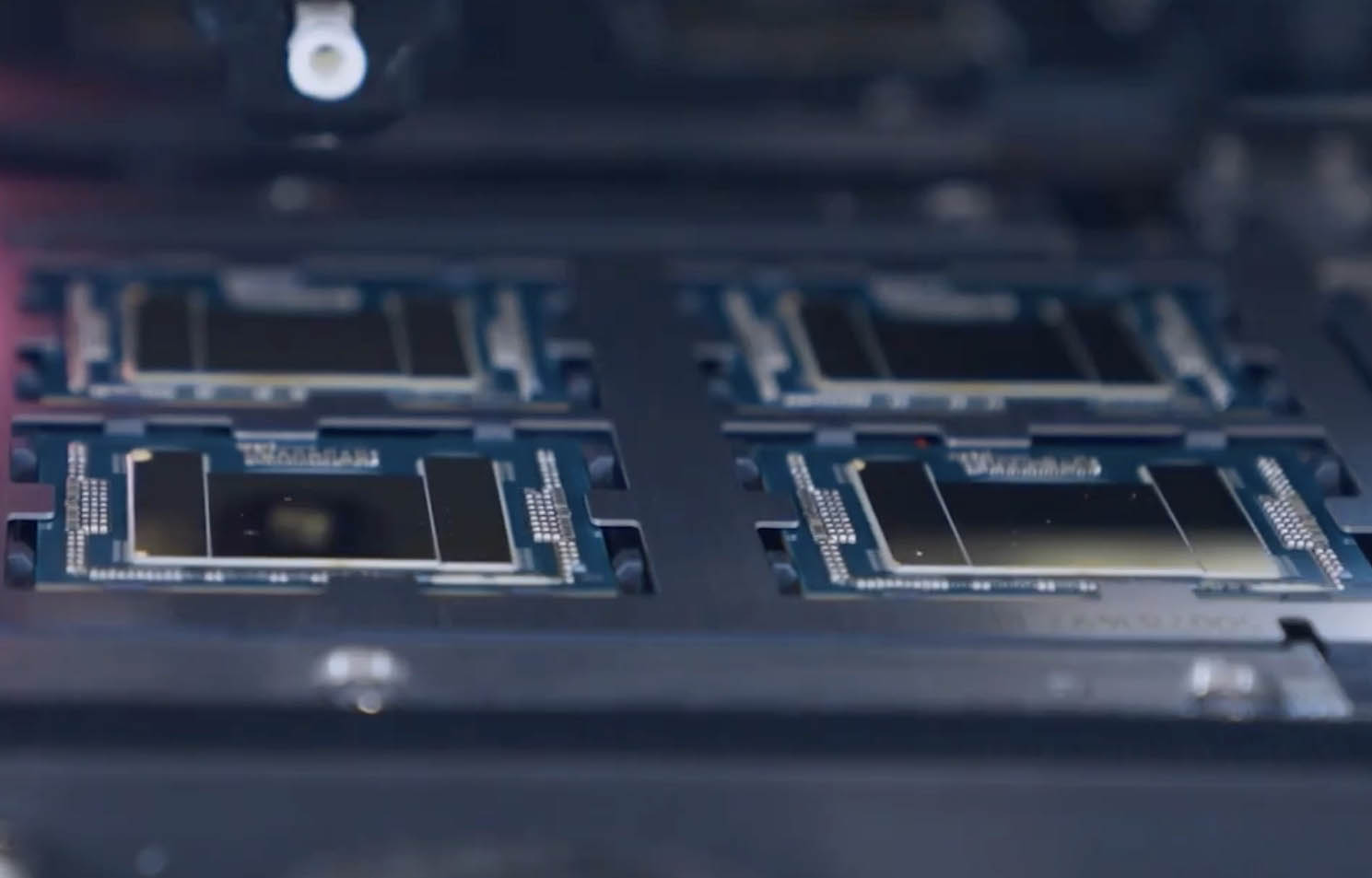

288 core SRF revealed, Intel sandbagging is a bit refreshing.

That's -AP, it uses 7529 package.Pat displays 288C SRF, yes, this is cleary SRF-SP.

As sandbagging as CL-AP or CPX-4 kek.Intel sandbagging is a bit refreshing.

That's -AP, it uses 7529 package.

esp on his 20% RWC IPC leak lolMild was right on all his intel leaks lol

That's -AP, it uses 7529 package.

As sandbagging as CL-AP or CPX-4 kek.

No, but it's a stillborn product and given that SRF-AP wasn't on the roadmaps...Oh if it's AP, it's basically vaporware.

Arrow lake is 20A confirmed 😄✅ .. lunar lake is looking good

Do you mean platform readiness of the Birchstream platform which is common between GNR and SRF?No, but it's a stillborn product and given that SRF-AP wasn't on the roadmaps...

Platform readiness lol

I hope that’s true but I wouldn’t bet on it. The only way that’s the case is if they can somehow get ARL-S to clock in the neighborhood of 5.4ghz.I am starting to think, that ARL performance estimates were like being Sierra Forrest 144C only -> designed to weed out rabid leakers.

If it is really on 20A, numbers we were "given" don't really make sense at all.

Anyway not long to wait, seems like 2024 is gonna be a year we all will drown in some Lake.

-AP and -SP are very different things for BHS.Do you mean platform readiness of the Birchstream platform which is common between GNR and SRF?

I have to give mild credit his intel leaks are rarely wrong.. intel engineers must trust himI am starting to think, that ARL performance estimates were like being Sierra Forrest 144C only -> designed to weed out rabid leakers.

If it is really on 20A, numbers we were "given" don't really make sense at all.

Anyway not long to wait, seems like 2024 is gonna be a year we all will drown in some Lake.