Lets do some very ROUGH math: The 40 core ICL die is 628 mm2 (according to Wikichip). The delidded SPR “tile” has been estimated to be 370mm2, and (in one of SPR configurations) there are four of them for a total of 1480mm2. 1480/628 is approx 2.35. 40 x 2.35 is 94 cores!! Of course the SPR core is bigger than ICL, but perhaps that‘s balanced by the uncore size of SPR, which is most likely not 2.35 that of ICL given that SPR is rumored to still be 8 DDR5 channels.

If the leaks are to be believed, SPR has the potential to match the rumored 96 cores of Genoa.

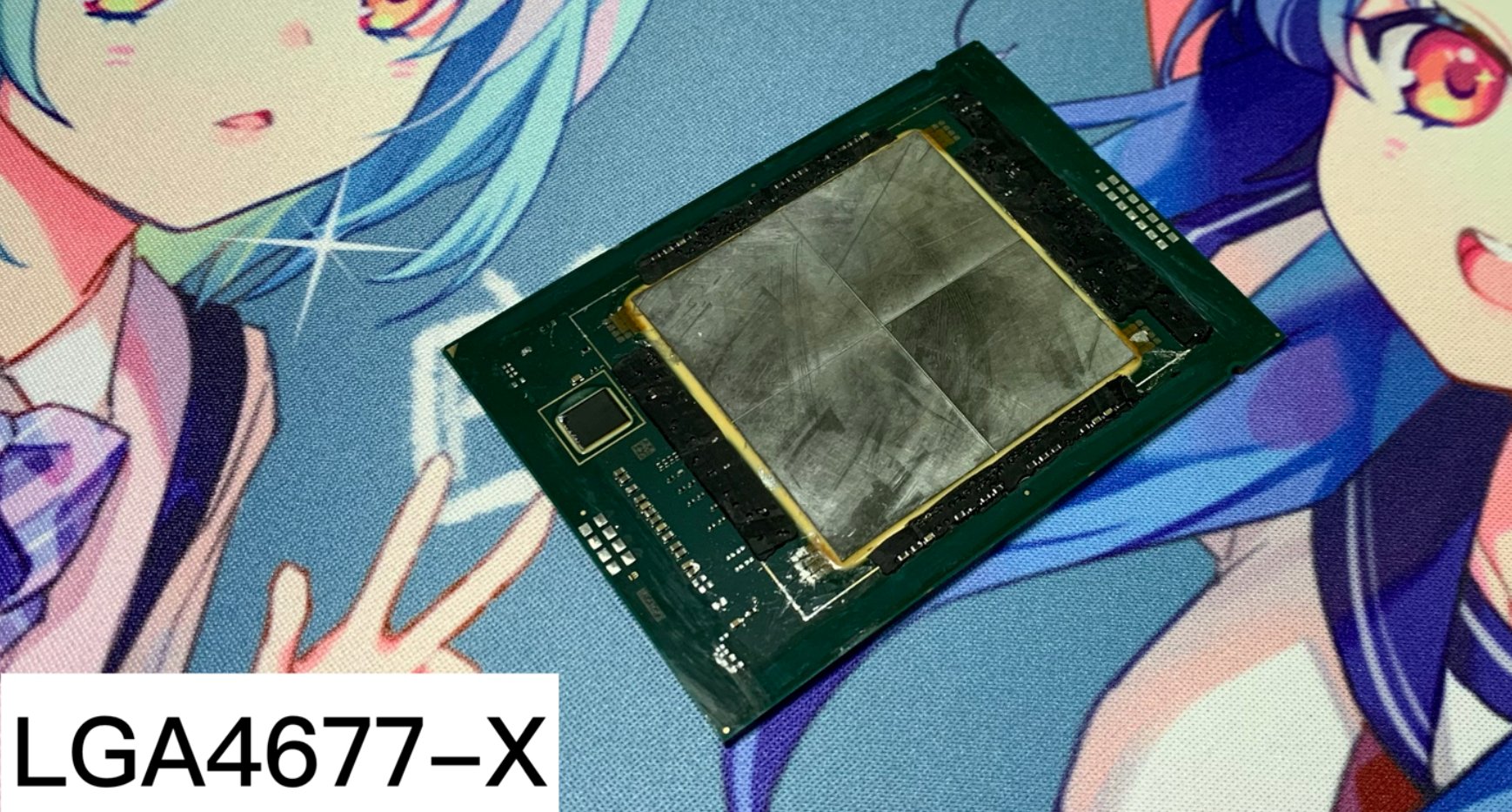

Quotes Quote Being a sample rather than a commercial product, the processor is marked as Intel Confidential and features the QVV5 sSpec, along with a 1.30 GHz frequency. The image was published by YuuKi_AnS, a known hardware leaker who sometimes has access to unreleased chips. We confirmed the CP...

linustechtips.com

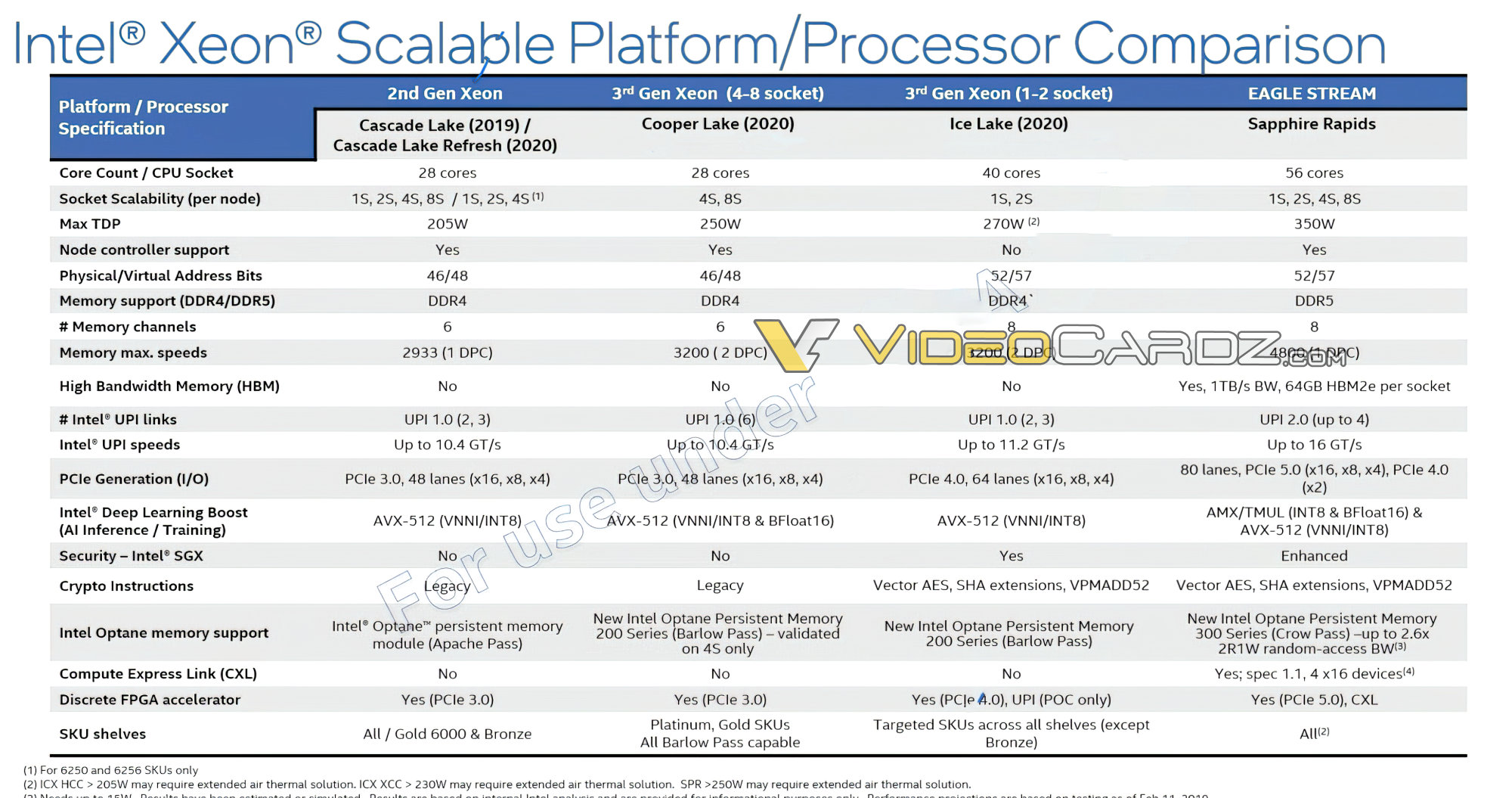

Intel launches its 3rd Generation Xeon Scalable, formerly Ice Lake. Fabricated on the company's 10nm process, those server chips go up to 40 Sunny Cove cores and offer a 20% IPC improvement over the prior generation.

fuse.wikichip.org