As difficult as it is to find a breaking point, there's no way P6 can span to Yonah.

That was really well said. You are probably right, that is a HUGE leap I made there! I think it may be best divided as P6 being Pentium Pro, Pentium II, Pentium III.

Then perhaps Core?

Pentium-M - Banias, Dothan, Yonah

Big changes internally here with pipe going 6 to 10 stages, micro-ops fusion, dedicated stack register management, SSE2/3 instructions

That would actually bridge nicely into the Core 2 generation so we'd have as follows.

Yes I think this make more sense. Pentium to Pentium Pro/PII/PIII to Core (Pentium-M) to Core2Duo (Conroe).

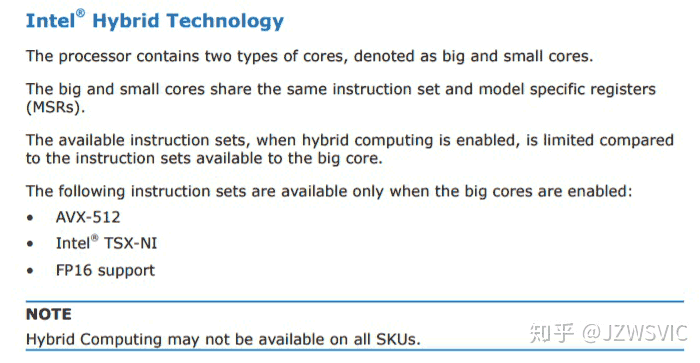

What do you think? So ADL would be Intel's 15th architecture.

1. 1978 - 8086 - I'm calling this the beginning of x86

2. 1982 - 80286 - Doubling of IPC, non-multiplexed buses, better prefetch, buffering, jumps

3. 1985 - 80386DX - 3 stage pipe, fully 32 bit, real/protected/virtual modes

4. 1989 - 486DX - Double IPC, on chip unified cache, on chip FPU, enhanced bus interface

5. 1993 - Pentium (P5) - 40% better IPC over 486 due mainly to superscaler design, better FP, separate data/instruction cache. I'm including everything from P5 to Tillamook in this generation.

6. 1995 - P6 (Pentium Pro, PII, PIII) - Speculative execution, OoO "dynamic" execution, Superpipeling 5 to 14 stages.

7. 2000 - Pentium 4 - Netburst, yeah, new architecture that didn't work out so well

8. 2003 - Core (Pentium M - Banias, Dothan, Yonah) - Pipeline going 6 to 10 stages, micro-ops fusion, dedicated stack register management, SSE2/3 instructions

9. 2006 - Core 2 (Conroe/Penryn) - Double IPC, Better OoO prediction, wider engine, smart cache, 128bit SSE

10. 2008 - Nehalem/Westmere - Macro-ops fusion better, loop stream detection, pipe goes to 16, new cache, better branch prediction, return of HT, on die memory controller (finally), turbo clocks

11. 2011 - Sandy/Ivy Bridge - New branch predictor, physical register file, better turbo, ring bus, micro-op cache, prefetcher improvement, fp/int improvement, MOV operation improvement

12. 2013 - Haswell/Broadwell - Wider execution engine, larger OoO buffer, better branch predictor, better/more in-flight loads, double cache bandwidth, better memory controller, 50% larger TLB

13. 2015 - Skylake(Sky/Kaby/KabyR/Coffee/Whiskey/Amber/Cannon/CoffeeR/Comet) - Wider front end, larger reorder buffer, more integer registers/in-flight stores, scheduler entries.

14. 2019 - Sunny Cove (Ice/Tiger/Rocket Lake) - 50% larger L1, double L2, larger reorder buffer, more in-flights loads/stores, better scheduler, 8 to 10 execution ports (wider back end), larger micro-op cache

15. 2021? - Alder Lake (Golden Cove/Gracemont) - Cool big/little cores that do stuff faster with less electron movement... hopefully