(Paper 29.1, “A 10nm High Performance and Low-Power CMOS Technology Featuring 3rd-Generation FinFET Transistors, Self-Aligned Quad Patterning, Contact Over Active Gate and Cobalt Local Interconnects,” C. Auth et al, Intel)

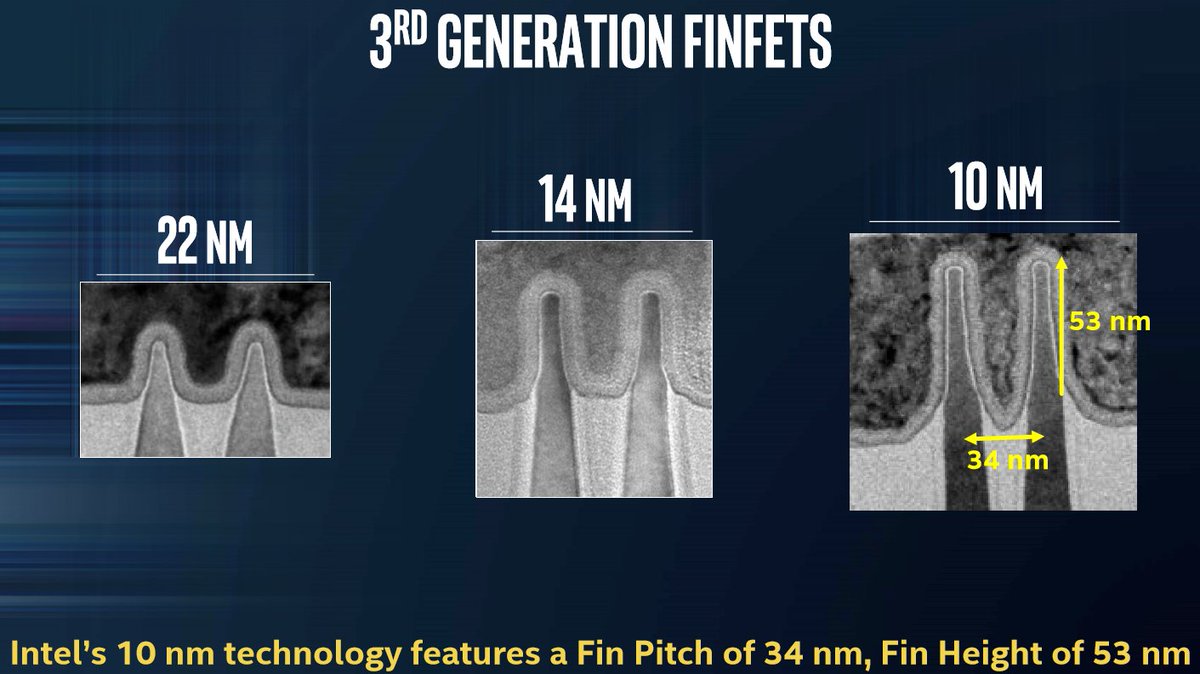

Intel researchers will present a 10nm logic technology platform with excellent transistor and interconnect performance and aggressive design-rule scaling. They demonstrated its versatility by building a 204Mb SRAM having three different types of memory cells: a high-density 0.0312µm2 cell, a low voltage 0.0367µm2 cell, and a high-performance 0.0441µm2 cell. The platform features 3rd-generation FinFETs fabricated with self-aligned quadruple patterning (SAQP) for critical layers, leading to a 7nm fin width at a 34nm pitch, and a 46nm fin height; a 5th-generation high-k metal gate; and 7th-generation strained silicon. There are 12 metal layers of interconnect, with cobalt wires in the lowest two layers that yield a 5-10x improvement in electromigration and a 2x reduction in via resistance. NMOS and PMOS current is 71% and 35% greater, respectively, compared to 14nm FinFET transistors. Metal stacks with four or six workfunctions enable operation at different threshold voltages, and novel self-aligned gate contacts over active gates are employed.

You can find the press kit at http://btbmarketing.com/iedm/

Intel researchers will present a 10nm logic technology platform with excellent transistor and interconnect performance and aggressive design-rule scaling. They demonstrated its versatility by building a 204Mb SRAM having three different types of memory cells: a high-density 0.0312µm2 cell, a low voltage 0.0367µm2 cell, and a high-performance 0.0441µm2 cell. The platform features 3rd-generation FinFETs fabricated with self-aligned quadruple patterning (SAQP) for critical layers, leading to a 7nm fin width at a 34nm pitch, and a 46nm fin height; a 5th-generation high-k metal gate; and 7th-generation strained silicon. There are 12 metal layers of interconnect, with cobalt wires in the lowest two layers that yield a 5-10x improvement in electromigration and a 2x reduction in via resistance. NMOS and PMOS current is 71% and 35% greater, respectively, compared to 14nm FinFET transistors. Metal stacks with four or six workfunctions enable operation at different threshold voltages, and novel self-aligned gate contacts over active gates are employed.

You can find the press kit at http://btbmarketing.com/iedm/