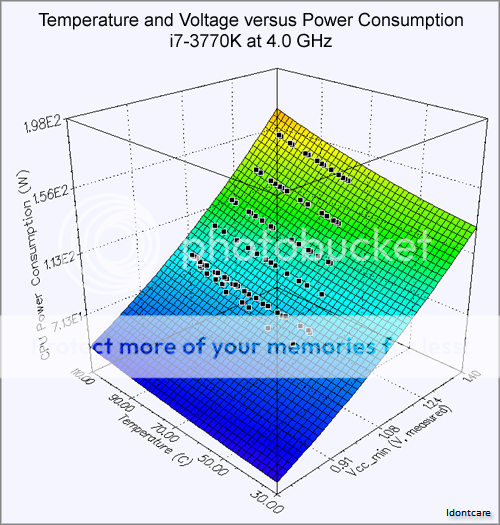

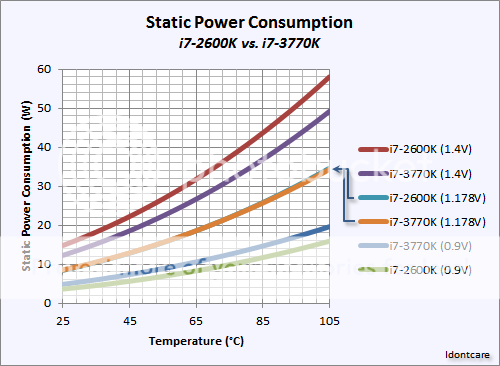

Yeah the static power was marginally improved with 22nm over 32nm, not too surprising considering that with the node shrink all the dielectric insulating layers got thinner.

Ordinarily we would have expected leakage to get worse, not better, but the Finfets really helped with that.

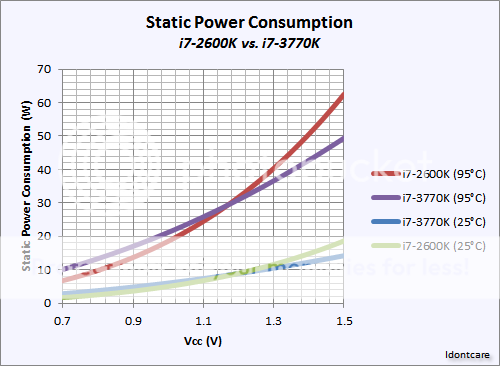

What really saved 22nm from a static leakage perspective is that Intel was able to scale-down the voltage needed to hit any given clockspeed. (clockspeed is not a factor in static leakage, only temperature and voltage are factors in static leakage)