Core logic density ain't nowhere near process limits with high clock targets. With different kind of design philosophy there might be density gains to be found in same process that just waits to be found.

The day's of big core logic density increases AND clock speed increases has long been over. Just look at the last 10 years. It's easy to see.

Worse than that, each new process not only yields decreasing improvements over the previous generation, it also costs increasingly (super linearly) more to make the tools, and more process steps (more expensive) than the previous step.

Sure, there are occasional jumps. Intel's new High NA machines they bought for an arm and a leg (and maybe a bit more) will provide a jump, but these are once in a decade (or more) jumps. You aren't going to get them every 18months, nor will you even get a true die shift every 18 months. More like 3 years right now, and I am guessing this will continue to lengthen out.

AMD ZEN has looked like this:

| Year | Zen Gen | Process Node (CCD) | CCD Size (mm²) | Max Clock (GHz) | Desktop Gain | Density ↑ vs Prior |

|---|

| 2017 | Zen | 14nm (GF) | ~213 (mono) | ~4.0 | — | — |

| 2018 | Zen+ | 12nm (GF) | ~213 (mono) | ~4.3 | ~+5–8% | ~+10–15% |

| 2019 | Zen 2 | 7nm (TSMC N7) | ~74 | ~4.7 | ~+12–15% | ~2.0× (~100%) |

| 2020 | Zen 3 | 7nm (TSMC N7) | ~80 | ~4.9 | ~+18–22% | ~0% (same node) |

| 2022 | Zen 4 | 5nm (TSMC N5) | ~72 | ~5.7 | ~+15–20% | ~1.8× (~80%) |

| 2024 | Zen 5 | 4nm (TSMC N4/N4P) | ~70–75 | ~5.7–5.8 | ~+5–12% | ~+6–10% |

| 2026–27 (est.) | Zen 6 | ~2nm (TSMC N2/N2P) | ~90–120 (est.) | ~6.2–6.5 (est.) | ~+15–25% (est.) | ~1.15–1.3× (~15–30%) |

Zen 3 was a fixed Zen 2 (Zen 2 move to chiplet design) so got a decent lift without a process change.

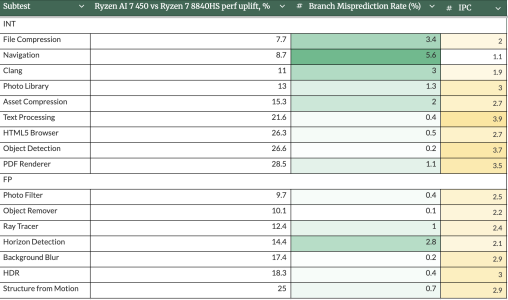

Look at Zen 5 though. With a 6-10% better transistor budget, it only got 5-12% IPC increase (not including server).... thus the "Zen 5%" criticism.

Zen 7 is essentially another Zen 5. It's a cleanup node for N2, not a big shrink. I wouldn't expect big IPC increases and only modest clock speed increases that are going to be mostly due to TSMC getting the process smooth on N2 class GAA.

It's just my opinion, but those thinking Zen 7 is going to be a big leap from Zen 6, I think you are setting yourselves up for disappointment.

The BIG change I see with Zen 7 is the move to higher core CCD's. I do kinda wonder how this is going to work out on desktop vs Intel's 52c NVL (Zen 7 with 32c/64t). I'm guessing that Intel still wins in Cinebench

😉.