IntelUser2000

Elite Member

- Oct 14, 2003

- 8,686

- 3,787

- 136

At one time I lost quite a bit of time trying to understand why my Toshiba laptop decided to idle at ~2-3W package power, with CPU cores in deep C state sleep but very low C2/C3 Package Residency.

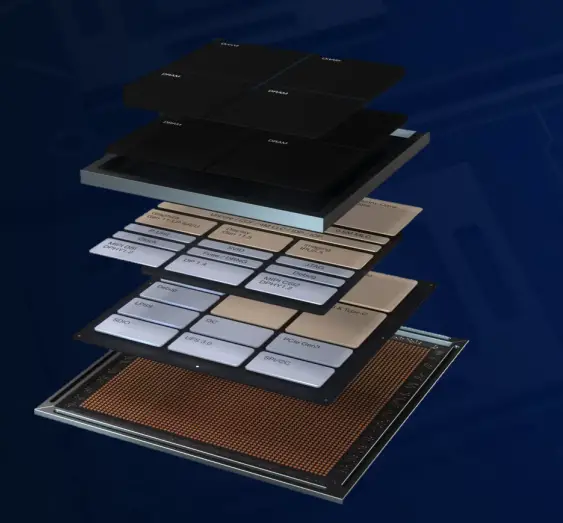

Using PoP DRAM should also mean the 7W TDP figure is more like 5W as DRAM can reach 2-3W according to NBC's HWInfo monitor, and being in same package means you have to account for DRAM into the figure for cooling. It may also be able to idle DRAM better as well, in addition to basically having an on-die PCH.

I know, I have a broken Clover Trail and a Bay Trail tablet. Just broken screens. I opened up the Clover Trail one up for fun and it had nothing but a single DRAM IC. I later realized it was the PoP DRAM.

The 8-inch BT device lasts 6-8 hours with a 15WHr battery and the 10-inch CT device lasts 7-9 hours with a 24WHr battery. Neither really has you caring about screen brightness, or shutting down applications and optimizing as much as I do on laptops/ultrabooks, because its just efficient.

There's a whole thread in NBR forum about laptop optimization. Some report going from 3 to 8 hours after optimization. Involves registry changes, updating every driver, not just from the manufacturer but from obscure sources and driver utilities, shutting down almost every non-essential services, and playing with throttlestop to make sure it works.

A single misbehaving application and/or hardware can triple the idle package power.