Finally someone agrees with meHere I was thinking SME2 would be core level.

Pathetic, cluster level accel is a benchmark hack, nothing more.

Discussion ARM Cortex/Neoverse IP + SoCs (no custom cores) Discussion

Page 58 - Seeking answers? Join the AnandTech community: where nearly half-a-million members share solutions and discuss the latest tech.

You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

adroc_thurston

Diamond Member

- Jul 2, 2023

- 8,201

- 10,942

- 106

Dear god the naming.

Unleashing Leading On-Device AI Performance and Efficiency with New Arm C1 CPU Cluster

The new Arm C1 CPU cluster, delivering unmatched on-device AI performance, power efficiency, and scalability for next-gen mobile devices.newsroom.arm.com

here

People should be shot for that.

Ahhh, they didn't replace Cortex branding so much as shorten it.

Unleashing Leading On-Device AI Performance and Efficiency with New Arm C1 CPU Cluster

The new Arm C1 CPU cluster, delivering unmatched on-device AI performance, power efficiency, and scalability for next-gen mobile devices.newsroom.arm.com

here

Interesting that they only increased it to v9.3-A tho.

This is a bit more detail...

www.arm.com

www.arm.com

Arm Lumex Compute Subsystem Platform

Redefining mobile AI with Arm Lumex Compute Subsystem Platform: On-device performance, immersive graphics, and developer-first tools.

C1-Ultra (Travis/X930):

developer.arm.com

developer.arm.com

C1-Premium (Alto?):

C1-Pro (Gelas/A730):

developer.arm.com

developer.arm.com

C1-Nano (Nevis/A530):

G1-Ultra (Drage):

developer.arm.com

developer.arm.com

G1-Premium:

developer.arm.com

developer.arm.com

G1-Pro:

C1-Ultra

C1-Ultra is Arm’s flagship Armv9.3 CPU, delivering best-in-class IPC, expanded caches, advanced prefetching, and low-latency pipelines.

C1-Premium (Alto?):

C1-Pro (Gelas/A730):

C1-Pro

C1-Pro is an Armv9.3 CPU delivering sustained performance in flagship CPU clusters when combined with C1-Ultra and C1-Premium cores, and serves as a high-performance big CPU in big.LITTLE clusters alongside the C1-Nano.

C1-Nano (Nevis/A530):

G1-Ultra (Drage):

Mali G1-Ultra

Mali G1-Ultra is Arm’s highest-performance GPU, featuring up to 16 shader cores and second-generation ray tracing (RTUv2) integrated per core.

G1-Premium:

Mali G1-Premium

High-performance GPU with optional RTUv2 and faster AI, bringing immersive gaming to premium smartphones with power efficiency.

G1-Pro:

PR blurb version...

newsroom.arm.com

newsroom.arm.com

Smarter, Faster, More Personal AI Delivered on Consumer Devices with Arm’s New Lumex CSS Platform, Driving Double-Digit Performance Gains

Arm introduces Lumex, its most advanced compute subsystem (CSS) platform for consumer devices, powering faster on-device AI, gaming, and real-time intelligence.

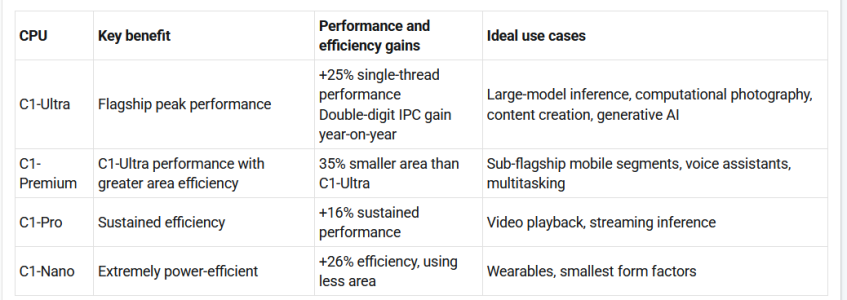

| CPU | Key benefit | Performance and efficiency gains | Ideal use cases |

| C1-Ultra | Flagship peak performance | +25% single-thread performance Double-digit IPC gain year-on-year | Large-model inference, computational photography, content creation, generative AI |

| C1-Premium | C1-Ultra performance with greater area efficiency | 35% smaller area than C1-Ultra | Sub-flagship mobile segments, voice assistants, multitasking |

| C1-Pro | Sustained efficiency | +16% sustained performance | Video playback, streaming inference |

| C1-Nano | Extremely power-efficient | +26% efficiency, using less area | Wearables, smallest form factors |

Seems I was right about Alto/C1-Premium being a ZenC like reduced area, near same flagship IPC core.

I wonder what devices it will end up in, and how that will play out in the Neoverse SKUs.

I wonder what devices it will end up in, and how that will play out in the Neoverse SKUs.

Amazing to see that they updated the naming in the documentation 1.5 years ago. And in that time no one rethought the decision.

But they have so many core types it's a lost battle. Most consumers aren't going to care or know. They may stick to "MediaTek bad, Exynos bad, Qualcomm good".

But they have so many core types it's a lost battle. Most consumers aren't going to care or know. They may stick to "MediaTek bad, Exynos bad, Qualcomm good".

The naming as Adroc said is terrible.

It should at least be consistent, which it really isn't as to me Pro sounds better than Premium.

Call the Nano core Micro instead, or perhaps even Kilo, saving the smol scale names like Micro and Nano for embedded or real time only.

Then Pro, Premium and Ultra can be Mega, Giga and Tera 🤘

My naming scheme probably isn't any better for the academic peasants out there tho 😂😆

It should at least be consistent, which it really isn't as to me Pro sounds better than Premium.

Call the Nano core Micro instead, or perhaps even Kilo, saving the smol scale names like Micro and Nano for embedded or real time only.

Then Pro, Premium and Ultra can be Mega, Giga and Tera 🤘

My naming scheme probably isn't any better for the academic peasants out there tho 😂😆

Core name should beThe naming as Adroc said is terrible.

It should at least be consistent, which it really isn't as to me Pro sounds better than Premium.

Call the Nano core Micro instead, or perhaps even Kilo, saving the smol scale names like Micro and Nano for embedded or real time only.

Then Pro, Premium and Ultra can be Mega, Giga and Tera 🤘

My naming scheme probably isn't any better for the academic peasants out there tho 😂😆

Core - A520

Ultra Core - A725

Ultron pro Max Core - X930

Here I was thinking SME2 would be core level.

Pathetic, cluster level accel is a benchmark hack, nothing more.

No, you guys simply don't understand. Look at M4 annotated die photos, the SME unit is HALF the size of a P core! It wouldn't be practical to include one that size in every core. So let's say you split it up and each P core got 1/4 of the SME capability. Your ST capability for SME suffers, and your MT capability is roughly the same. I guess you'd call that a win? If so you ignore that the cost is that to fully exploit it ALL FOUR CORES are busy!

With the separate unit you can get the entire cluster's worth of SME performance with just one core, leaving the other three cores free to do other stuff. That's a clear and undeniable win.

These matmul instructions aren't something where you might slip in just a few instructions worth here and there like NEON/SSE/AVX512. It is only going to be used for longer sequences - the kind of stuff that previously was kicked off to a GPGPU (if you needed enough of it and were willing to deal with the hassle) or more often run slower using existing FP capability. There is no benefit to having SME in each core, if the cost is that each core has less of it.

The only people calling it a "benchmark hack" are people reaching and grasping at straws for excuses why AVX512 acceleration is A-OK but SME is not. They're butthurt because ARM is finally benefitting from special instructions which used to be a great way to make x86 score better on benchmarks without programs using the traditional instructions that have existed for many years benefiting nearly as much.

Intel AMX exists and it is per core. SME is a benchmark hack for Single Core if it's not part of the core why don't they show us the SPEC Score instead of memebench with a generic GCC -O2 with same compiler.The only people calling it a "benchmark hack" are people reaching and grasping at straws for excuses why AVX512 acceleration is A-OK but SME is not. They're butthurt because ARM is finally benefitting from special instructions which used to be a great way to make x86 score better on benchmarks without programs using the traditional instructions that have existed for many years benefiting nearly as much.

Intel AMX exists and it is per core. SME is a benchmark hack for Single Core if it's not part of the core why don't they show us the SPEC Score instead of memebench with a generic GCC -O2 with same compiler.

So if instead of making SME per cluster they had one core that was SME enabled in each cluster you'd be fine with it? Or would you say "it only counts if ALL the cores have it", because you're just going to look for any reason to not count something that helps ARM be faster than your beloved x86?

This is the reason I only care about comparisons on the clang subtest, or gcc on SPEC. Then none of the SIMD bs counts, only the same type of real instructions that a compiler is generating not hand coded sequences. If a compiler can generate AVX512 code in the clang subtest more power to it!

You have to pass AVX512 or x86_64V4 falg for Clang to generate AVX-512 if you don't pass that it won't generate AVX-512. That's why I said generic O2 Compile.So if instead of making SME per cluster they had one core that was SME enabled in each cluster you'd be fine with it? Or would you say "it only counts if ALL the cores have it", because you're just going to look for any reason to not count something that helps ARM be faster than your beloved x86?

This is the reason I only care about comparisons on the clang subtest, or gcc on SPEC. Then none of the SIMD bs counts, only the same type of real instructions that a compiler is generating not hand coded sequences. If a compiler can generate AVX512 code in the clang subtest more power to it!

And I meant either all core should support or it shouldn't count as ST.

Nowadays it's "Mediatek offer better value", "Qualcomm overpriced", "Exynos overheat"Amazing to see that they updated the naming in the documentation 1.5 years ago. And in that time no one rethought the decision.

But they have so many core types it's a lost battle. Most consumers aren't going to care or know. They may stick to "MediaTek bad, Exynos bad, Qualcomm good".

I'd rather it's per cluster and not wasted space on the cores when it's not in use.Intel AMX exists and it is per core. SME is a benchmark hack for Single Core if it's not part of the core why don't they show us the SPEC Score instead of memebench with a generic GCC -O2 with same compiler.

It's only a benchmark hack because a certain benchmark used it as part of its generic score and doesn't include the score without it.

Now that we all know about it the benchmark is exposed as pandering at best.

Than don't potray it as a part of Single Core performance which GB is doing.I'd rather it's per cluster and not wasted space on the cores when it's not in use

ToTTenTranz

Senior member

- Feb 4, 2021

- 895

- 1,497

- 136

Looks like C1-Nano is the only LITTLE core they'll release, so it replaces everything from A520 to A320 and all the A53 being used in smartwatch SoCs.So, A5XX is nano, where A3XX is then? Pico?View attachment 129936

tbh I'm not that bothered by it.Than don't potray it as a part of Single Core performance which GB is doing.

It's not like the average buyer is ever going to look that closely (or even needs as much CPU perf as they can get today), and the more discerning crowd like us know the problem exists anyway.

I'm more interested in a deep dive IPC and perf/watt testing round to see where the new cores stand, as the ARM PR slides are utterly terrible and uninformative.

We got a meme slide in name of IPC and performance per wattm more interested in a deep dive IPC and perf/watt testing round to see where the new cores stand, as the ARM PR slides are utterly terrible and uninformative.

The Exynos thing seems more a result of Samsung's never ending fab node woes.Nowadays it's "Mediatek offer better value", "Qualcomm overpriced", "Exynos overheat"

The semicon design team tried to make a deal with TSMC to fab Exynos but they would rather just give Sammy the middle finger even though they are fabbing Intel who are threatening to be a better fab competitor (at least in tech if not partnership competency) than Samsung.

Precisely, sick of this from ARM.We got a meme slide in name of IPC and performance per watt

Eventually someone will measure it properly with benchmarks and voltmeters so there's no point in trying to obfuscate the facts with PR that doesn't functionally matter to people that actually buy ARM based products.

Interesting, so Nano is being pushed out of the mainstream?Looks like C1-Nano is the only LITTLE core they'll release, so it replaces everything from A520 to A320 and all the A53 being used in smartwatch SoCs.

Oh boy... so in some years, all the phones might end with processors with all out of order cores like Dimensity 9300?

TRENDING THREADS

-

Discussion Zen 5 Speculation (EPYC Turin and Strix Point/Granite Ridge - Ryzen 9000)

- Started by DisEnchantment

- Replies: 25K

-

Discussion Intel Meteor, Arrow, Lunar & Panther Lakes + WCL Discussion Threads

- Started by Tigerick

- Replies: 24K

-

Discussion Intel current and future Lakes & Rapids thread

- Started by TheF34RChannel

- Replies: 23K

-

-

AnandTech is part of Future plc, an international media group and leading digital publisher. Visit our corporate site.

© Future Publishing Limited Quay House, The Ambury, Bath BA1 1UA. All rights reserved. England and Wales company registration number 2008885.