Yes they seem to get around a bit, probably a necessity given they make their money by IP rather than physical product.It seems to be an academic event sponsored by ARM.

-

We’re currently investigating an issue related to the forum theme and styling that is impacting page layout and visual formatting. The problem has been identified, and we are actively working on a resolution. There is no impact to user data or functionality, this is strictly a front-end display issue. We’ll post an update once the fix has been deployed. Thanks for your patience while we get this sorted.

You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

Discussion ARM Cortex/Neoverse IP + SoCs (no custom cores) Discussion

Page 55 - Seeking answers? Join the AnandTech community: where nearly half-a-million members share solutions and discuss the latest tech.

poke01

Diamond Member

Oh good, jumping straight to SME2.

Soon it will be useful beyond Geekbench scores.

“The SME2-enhanced performance in your applications will then be portable across Arm-based platforms from iOS and iPadOS to MacOS and Android.”

View attachment 126940

This might be when they announce...

newsroom.arm.com

newsroom.arm.com

Arm Announces Earnings Release Date for First Quarter Fiscal Year Ended 2026

Arm (NASDAQ:ARM) will report financial results for the first quarter of fiscal year 2026 on July 30, 2025 after market close.

Oh good, jumping straight to SME2.

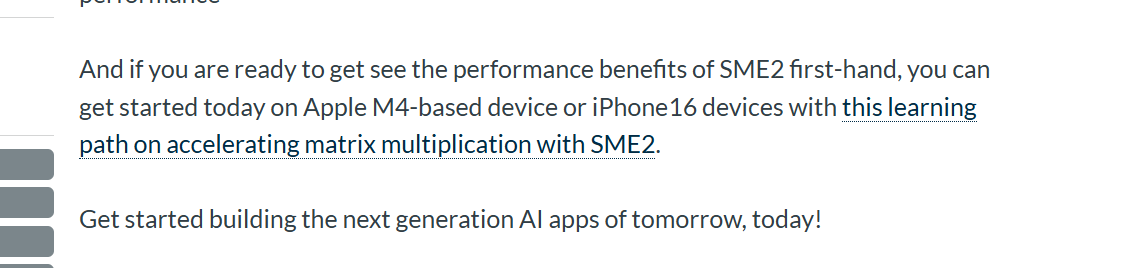

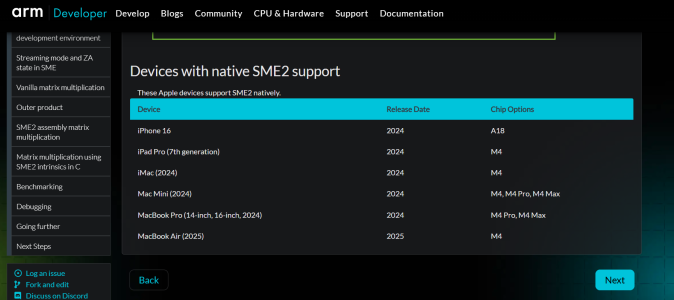

SME2 is what M4/A18 currently support and was introduced by ARM in 2022. Not sure why ARM is hyping it now, other than because "AI".

poke01

Diamond Member

They are hyping it now cause it will finally be supported by ARMs cores this year.SME2 is what M4/A18 currently support and was introduced by ARM in 2022. Not sure why ARM is hyping it now, other than because "AI".

but not Windows? Curious.Arm-based platforms from iOS and iPadOS to MacOS and Android.”

Io Magnesso

Senior member

In the first place, it is called an accelerator or a coprocessor that is shared.They are hyping it now cause it will finally be supported by ARMs cores this year.

It's strange that the SME is used for single-thread benchmarks.

Io Magnesso

Senior member

That's what is said to be the bulk of the score.In the first place, it is called an accelerator or a coprocessor that is shared.

It's strange that the SME is used for single-thread benchmarks.

I'm not saying that SME is bad, it's a complaint about the Geekbench.

Io Magnesso

Senior member

If so, I think it would be good to increase the percentage of the score to AVX512 as well...That's what is said to be the bulk of the score.

I'm not saying that SME is bad, it's a complaint about the Geekbench.

It's kind of unfair...

In the first place, it is called an accelerator or a coprocessor that is shared.

It's strange that the SME is used for single-thread benchmarks.

That's how Apple implemented it, but nothing says ARM will do the same. In fact, I think it is unlikely they would do that, because they design CORES not SoCs so designing SME as something separate from the core would be a sea change in the way they do things. Not saying it is impossible, but SME2 is defined in the ARMv9 ISA as specific instructions just like SVE. Just like AVX512 - which could be implemented in the way Apple implemented SME if AMD or Intel had chosen to. They just don't have any experience doing anything like that since the 386 days when the FPU was available as a separate co-processor chip.

poke01

Diamond Member

Apples own docs say sme2 support is available. As well Geekbench reports sm2 in the logs.I thought M4 support SME only. Any other source mention that M4 supporting SME2 beside today announcement???

SME2 is part of ARMv9.4 and from the Wiki M4 uses ARMv9.2

Io Magnesso

Senior member

I know what you meanThat's how Apple implemented it, but nothing says ARM will do the same. In fact, I think it is unlikely they would do that, because they design CORES not SoCs so designing SME as something separate from the core would be a sea change in the way they do things. Not saying it is impossible, but SME2 is defined in the ARMv9 ISA as specific instructions just like SVE. Just like AVX512 - which could be implemented in the way Apple implemented SME if AMD or Intel had chosen to. They just don't have any experience doing anything like that since the 386 days when the FPU was available as a separate co-processor chip.

Apple shares SME units across multiple cores, like an accelerator (coprocessor)

Apple has implemented it that way, but we still don't know how other ARMs will implement it.

I thought M4 support SME only. Any other source mention that M4 supporting SME2 beside today announcement???

SME2 is part of ARMv9.4 and from the Wiki M4 uses ARMv9.2

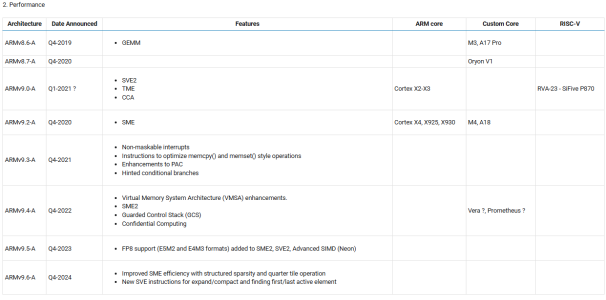

SME is defined in ARMv9.2, SME2 is defined in ARMv9.3, SME2p1 is defined in ARMv9.4, a bunch of specific named additions to SME (shades of the Intel confusion around AVX512 🙄 ) are defined in ARMv9.5, and SME2p2 is defined in ARMv9.6.

Apple's M4 patches to LLVM/clang define it as ARMv8.7. I think I remember seeing claims there was something that's mandatory in ARMv9 that Apple hasn't implemented so they can't call it ARMv9 - maybe that's SVE but I'm 99% sure that SVE isn't strictly required in ARMv9. Now of course SME2 is not part of any ARMv8 iteration, but supporting MORE than the spec requires isn't really a problem I suppose.

Io Magnesso

Senior member

It's a hassle... AVX512 is also mostlySME is defined in ARMv9.2, SME2 is defined in ARMv9.3, SME2p1 is defined in ARMv9.4, a bunch of specific named additions to SME (shades of the Intel confusion around AVX512 🙄 ) are defined in ARMv9.5, and SME2p2 is defined in ARMv9.6.

Apple's M4 patches to LLVM/clang define it as ARMv8.7. I think I remember seeing claims there was something that's mandatory in ARMv9 that Apple hasn't implemented so they can't call it ARMv9 - maybe that's SVE but I'm 99% sure that SVE isn't strictly required in ARMv9. Now of course SME2 is not part of any ARMv8 iteration, but supporting MORE than the spec requires isn't really a problem I suppose.

Damn confusing. Guess my table is not comprehensive enough for all versions of SME 😳SME is defined in ARMv9.2, SME2 is defined in ARMv9.3, SME2p1 is defined in ARMv9.4, a bunch of specific named additions to SME (shades of the Intel confusion around AVX512 🙄 ) are defined in ARMv9.5, and SME2p2 is defined in ARMv9.6.

Apple's M4 patches to LLVM/clang define it as ARMv8.7. I think I remember seeing claims there was something that's mandatory in ARMv9 that Apple hasn't implemented so they can't call it ARMv9 - maybe that's SVE but I'm 99% sure that SVE isn't strictly required in ARMv9. Now of course SME2 is not part of any ARMv8 iteration, but supporting MORE than the spec requires isn't really a problem I suppose.

Io Magnesso

Senior member

Which is the ARM ISA version of Apple's 2024 CPU? Which one?

There is a possibility that ARM is simply arbitrarily grouped into SME2 but There is also the possibility of ordinary SME

Damn confusing. Guess my table is not comprehensive enough for all versions of SME 😳

View attachment 126988

That table is wrong. ARM's own site clearly shows ARMv9.3 is where SME2 was defined:

https://developer.arm.com/documenta...scriptions/The-Armv9-3-architecture-extension

It also has links to all the ARMv8 and ARMv9 extensions to see what was added when.

EDIT: if you look at the ARMv9.2 tab at the very bottom it lists a bunch of optional features added in later releases of ARMv9.2. One of them is SME2p1 (i.e. the version of SME defined in ARMv9.4)

Last edited:

Apples M4 core is v9.2A. It’s in their cpu optimisation guide

It was originally defined as ARMv8.7 in LLVM. I dug up the patch Apple submitted for that, it shows why:

+ // Technically apple-m4 is ARMv9.2a, but a quirk of LLVM defines v9.0 as

+ // requiring SVE, which is optional according to the Arm ARM and not

+ // supported by the core. ARMv8.7a is the next closest choice.

Rockchip unveils RK3668 10-core Arm Cortex-A730/Cortex-A530 SoC with 16 TOPS NPU, RK182X LLM/VLM co-processor - CNX Software

The Rockchip Developer Conference 2025 (RKDC!2025) is now taking place in Fuzhou, China, with some interesting announcements such as the Rockchip RK3668

www.cnx-software.com

www.cnx-software.com

NEw Rockchips SoC underway, the RK3688 and RK3668. With unannounced Cortex A730/A530 and also unnanounced ARM Magni GPU.

TRENDING THREADS

-

Discussion Zen 5 Speculation (EPYC Turin and Strix Point/Granite Ridge - Ryzen 9000)

- Started by DisEnchantment

- Replies: 25K

-

Discussion Intel Meteor, Arrow, Lunar & Panther Lakes + WCL Discussion Threads

- Started by Tigerick

- Replies: 25K

-

Discussion Intel current and future Lakes & Rapids thread

- Started by TheF34RChannel

- Replies: 24K

-

-