Cogman

Lifer

- Sep 19, 2000

- 10,286

- 147

- 106

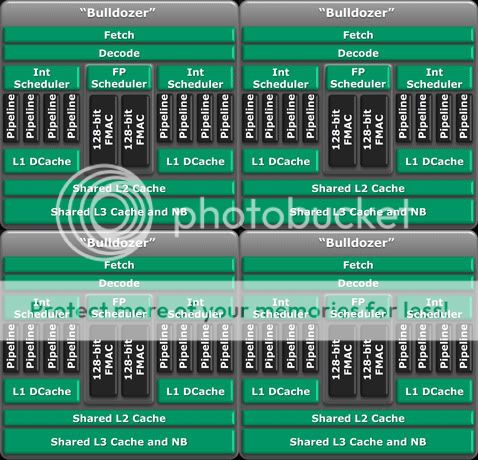

Point taken.JH has said not to read too much into the implied architectural limitations one might divine from sifting the tea leaves of the power-point slideware and diagrams (I am paraphrasing of course) and I completely agree with him.

It might appear to you and me that the fetch unit is simplistic and potentially limiting, but we would be doing ourselves a disservice to assume the power-point slide fully represents the attributes and capabilities of the fetch unit. (or any other architectural unit for that matter)

We take these diagrams to mean "at a minimum this much can be assumed to be true/guaranteed". With that initial condition, plus a few boundary conditions, we can set about parsing thru the ODE's that underlie our organic-based speculation processing units.

I guess the one thing that we can tell from the slides and comments is that Bulldozer is going to be a significant change from the phenom architecture. Time will tell if this will be a good change.