If that were the case that would probably mean they would be porting some mystery GPU architecture to these nodes. Such architecture they would probably also license to other companies (which probably would be making products like risc-v or acorn family SoC's). What GPU architecture would be a good candidate for this? Would they have probems licensing (in the next few years) Navi because it's too leading edge?

CPU = CMT-based with Linear IPC/power&area cores (Bobcat/Jaguar/Mongoose-esque)

GPU = Something in between CDNA(Compute/Tensor&Matrix) and RDNA(Gaming/Packed&Ray-tracing), with Tiny CUs/Small WGP.

Fabric = AMD Infinity Fabric

Multimedia = Cadence Xtensa+AMD?/HiFi 5

DDR&I/O = Cadence and/or Synopsys

What we are waiting for before AMD pulls the trigger:

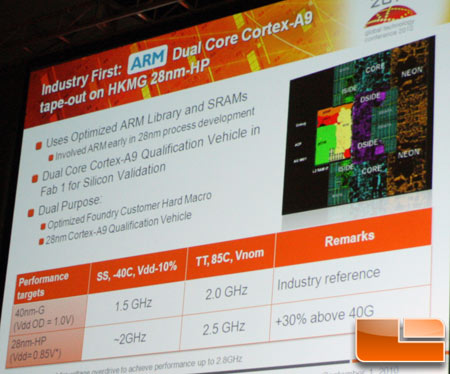

1. 22FDX++ which uses new 12FDX transistors, FDX nodes are FEOL asymmetric. So, FEOL can be shared across BEOL nodes; (22FDX = 14FD FEOL, 22-28nm BEOL)

2. More modern variants of I/O-support; DDR5/LPDDR5/PCIE5/USB4 specifically from Synopsys

First launch 22FDX++ (DDR4) -> Second launch 22FDX+++ (DDR5), same die different transistors and enablement. Much like how Carrizo-variants were DDR3-orientated and Bristol-variants were DDR4-orientated. DDR4 is the most cost-efficient and most available currently, which might be held till 2024~2026.

3. 22FDX++ has to be available at Fab 1 and Fab 7, Sempron's home fabs;

With Fab 8 as third source internal source.

Singapore + Pasir Ris = GloFo's biggest fab and SOITEC's biggest SOI wafer fab

Dresden + Bernin II = GloFo's second biggest fab and SOITEC's second biggest SOI wafer fab

Malta + St Peters = GloFo's smallest fab and GlobalWafer's local area SOI, unknown capacity for now.

SOITEC has a 3rd SOI fab in the works, and I expect given ~$4B+ wherever that fab is where GloFo will drop a 4th fab near it.

On one: 22FDX/22FDX+ = Lg20/14FD transistors w/ 22FDX being BOX20 and 22FDX+ being BOX15

22FDX++ = Lg15/10FD-12FDX transistors w/ 22FDX++ being strained BOX15 w/ 12FDX.

CTI path (like 90nm/65nm):

Node - Intro Year at Fab (not to customers)

22FDX - 2016 /Gen1

22FDX - 2017 /Gen2

22FDX - 2018 /Gen3

22FDX - 2019 /Gen4

22FDX+ - 2020 /Gen5

22FDX+ - 2021 /Gen6

22FDX++/12FDX - 2022 /Gen7

22FDX++/12FDX - 2023 /Gen8

22FDX moves away from logic improvement(if it was 90nm/65nm, but 22FDX/12FDX would be closely related in reality and continue at the same time)

12FDX - 2024 /Gen9

FDX is heavily CTI'd at GloFo similar to 90nm/65nm generation

https://www.anandtech.com/show/2018

AMD enters at the end of logic improvement, rather at the beginning with the given trailing edge focus. Which gives highest performance&yield and lowest power&cost since it isn't intro-ing into a node when it is bad.

Assumptions;

CPU: CMT-Mode0 where replicating cores aren't a concern; Distributed, but shared Retire/Rename/PRF/Load-Store.

- Zen-like CMP-mode(Mode0p1), Zen-like SMT2-mode(Mode0p0), Excavator-like CMT2-mode(Mode1p0)

Rather than extra-wide monolithic structures, distributed less-wide structures are more efficient (maximize linear IPC-gain via replicated small-IPC superscalar pipeline structures)

GPU: Requirements probably need software work to be able to scale up to RDNA or CDNA. So compatibility to both is probably a need.

- G-series sells on CDNA-esque scale up, Sempron sells on RDNA-esque scale up.

CDNA-esque - Small-SIMD or Matrix Wavefront Compute => CDNAx Big-SIMD and Matrix Wavefront Compute,etc

RDNA-esque - Thinner Memories, Packed-SIMD Wavefront+RT Gaming => RDNAx Wider Memories, Packed-SIMD Wavefront+RT Gaming, etc

Everything else: Probably a requirement to support modern implementations, hence Infinity Fabric(rather than non-coherent Garlic and coherent Onion) and HiFi 5.

- Up to date system IP on-par with latest Zen SoC gen. <--- Minimal area gain, since Fixed Function has Fixed clocks, 22FDX-8T -> 22FDX++-6T at trailing edge implementation is a thing.

Node:

22FDX dev. cost is less than 14LPP/12LP+ for low ASP sub-$40 SoC (minus 30-40M$)

22FDX prod. cost is less than 14LPP/12LP+, ... (approximately minus 2000$ per wafer)

22FDX manufacturing capacity is heading multi-fab capable while 12LP+ is just Module 1 at Fab 8. (More fabs, less risk)

22FDX has more customers thus more IP options for semi-custom. (More customers, more markets to grow for semi-custom)

Exact-ish launch schedule based on a ray:

E2-9000e(2Q2017) -> 3015e(3Q2020)[reduced supply, reduced profit margin] -> 22FDX APU(4Q2023)

Which matches with named product launch ray:

Stoney(2016) -> Pollock(2020) -> 22FDX APU(2024)

Which gives AMD adequate time:

1. Strain SOI integration (+1.5 times freq, for unstrained 22FDX -> +2 times freq, for strained 22FDX)

2. Any 22FDX next-gen/plusplus w/ finer CPP and denser interconnect like Intel's 22FFL++ and Samsung's 17LPV.

3. If the ray goes on allows for 12FDX+ to go to a cost-reduced lithography: Late Standard-NA EUV(eliminate double patterning) or low-energy 6-cluster JFIL(more energy(fab-operation cost)/cost(tool-depreciation) efficiency). Which would go to the finer CPP and denser interconnect for 12FDX given 1Q27~2028.

There is also the semi-custom avenue being cheaper on the Geode/G-series lineup.

-> Wired router (OPNSense, PfSense)

-> Wireless router (OpenWRT)

-> Aerospace (re-design for Space-hard, and RISC-V to insert into Am29000-successor market)

-> Processor(22FDX)+FPGA(22FDX)

Allowing for a leapboard if successful to 6nm/4nm semi-custom

-> >4-port >10Gig wired

-> 16x16 WiFi 7/802.11be

-> ARM-premium (re-design for Space-tolerent)

etc

After calculating a bit(over several days) and guessing new titlenames based on Linkedin profiles;

Opteron Essentials => 4 modules; 4 CPU cores(SMT/CMP-mode) or 8 CPU cores(CMT-mode):: <$50USD, 9.9W TDP

Radeon Essentials => 384 32-bit ALU or equivalent:: <$50USD, 9.9W TDP

Sempron/G-series => 2 Modules, 192 32-bit ALUs or equivalent:: <$30 USD, 7.5W(SP1), 5W(SP2), ~3W(G1), ~1.5W(G2).

Reduced Die-cost

Reduced Package-cost

Reduced Systems-cost

Reduced Power-cost

etc.

====

Edit(April 2022): New GlobalFoundries stuff...

It is potentially a 3D Ultra-low-power SoC, numbers/stats above are somewhat accurate.

Stack-A: IODx (DDR5 PHY), CPUx(mid-die), CPUx(top-die) ==> Opteron Essential

Stack-B: IODy (LPDDR5 PHY), GPUx(mid-die), CPUx(top-die) ==> Sempron Essential

Stack-C: IODy (LPDDR5 PHY), GPUx(mid-die), GPUx(top-die) ==> Radeon Essential

Rather than a planar 100mm^2, it is likely to be a 50-75 mm2 with Z-height, etc.

12FDX is used for compatibility with 12LP-3D Logic/Logic process. As well as having the best density/performance given the price. With 12FDX being at least ~$1000 cheaper than 12LP/12LP+.

en.wikipedia.org

en.wikipedia.org