So what are we going to use the extra pins for? (387 pins)

If we assume (I don't know) that 2/3 are power supply pins on AM4 and AM5 increase power to 120W from 105W then we need about 130 extra pins.

(feel free to count https://www.docdroid.net/6cDW11N/am4-pinout-diagram-pdf)

Still about 250 left.

The number of pins for the DDR interface is about the same I think (DDR4 vs DRR5)

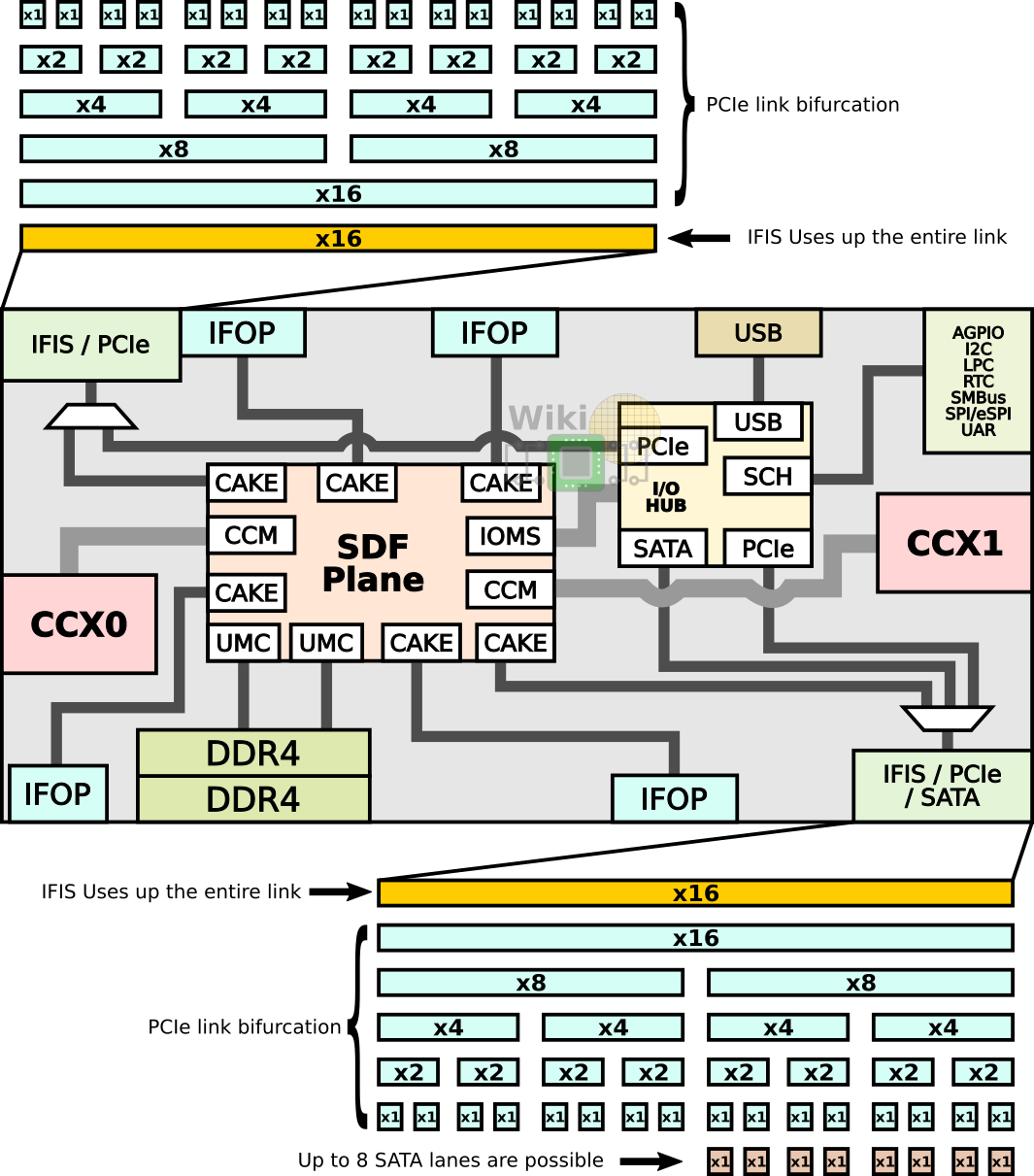

PCI-E 5 they can add more lanes let say 32 extra pins.

A few more USB lets say 20 extra pins.

So still more than half left of the new extra pins?

(I assume they don't add more than 200 pins just not to use them.)

Maybe even higher TDP 140W...(that would use up all pins)

If we assume (I don't know) that 2/3 are power supply pins on AM4 and AM5 increase power to 120W from 105W then we need about 130 extra pins.

(feel free to count https://www.docdroid.net/6cDW11N/am4-pinout-diagram-pdf)

Still about 250 left.

The number of pins for the DDR interface is about the same I think (DDR4 vs DRR5)

PCI-E 5 they can add more lanes let say 32 extra pins.

A few more USB lets say 20 extra pins.

So still more than half left of the new extra pins?

(I assume they don't add more than 200 pins just not to use them.)

Maybe even higher TDP 140W...(that would use up all pins)