-

We’re currently investigating an issue related to the forum theme and styling that is impacting page layout and visual formatting. The problem has been identified, and we are actively working on a resolution. There is no impact to user data or functionality, this is strictly a front-end display issue. We’ll post an update once the fix has been deployed. Thanks for your patience while we get this sorted.

You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

Question Alder Lake - Official Thread

Page 48 - Seeking answers? Join the AnandTech community: where nearly half-a-million members share solutions and discuss the latest tech.

TESKATLIPOKA

Platinum Member

Are you sure you tested 2C+6c? You have a 12700k which is 8C+4c core, right?I did run the test in 2+6 configuration and the result was pretty good. Have a look at the updated chart: https://forums.anandtech.com/thread...k-your-system-new-benchmark-criteria.2588294/

Or you actually meant 6C+2c?

TheELF

Diamond Member

Ryzen increased the roof for sale price of the desktop cpu from $300 to $500, which allowed intel to steadily increase their prices up and above that point, even if they would have less sales due to smaller marketshare ,which they don't, less sales at a higher price is still more money as long as the price increase is higher than the loss in sale numbers.I hope you or someone else will help me understand how that works. How does Intel sell more CPUs if their competitor is thriving and taking away market share from them?

For intel they made twice the money right after ryzen released and continue to keep making twice the money up to this day.

Yeah, as you said before it's breakup, how much money is intel going to be able to make if they split them up?Monopolies are often bad for consumers, and innovation, but they are great for raking in money.

Ask Standard Oil, American Steel, and yes AT&T which was the most profitable company in the world before it's breakup.

So I'm really not getting the far less money argument, using AT&T as an example.

My guess is that intel doesn't want to find that out, under any circumstance.

Heartbreaker

Diamond Member

Yeah, as you said before it's breakup, how much money is intel going to be able to make if they split them up?

My guess is that intel doesn't want to find that out, under any circumstance.

Even if AMD went away, there wouldn't be much case for splitting up Intel.

Hulk

Diamond Member

Are you sure you tested 2C+6c? You have a 12700k which is 8C+4c core, right?

Or you actually meant 6C+2c?

Sorry I tested 2+4.

But then also if you see a lion every other day, you see half a lion every day.Dead AMD = ( intel = at&t )

= far less money, if any at all

Also look at the money intel made before ryzen and after,

healthy amd = moar money

A 16 core epyc chip masquerading as a desktop processor? Clearly, the 5950x has been caught with its pants down in these iconic productivity tests? Look at how much ground it gives up in AUTOCAD to an i5! Not to speak of even trading blows with an i5 in Adobe suite. These tests clearly show the 5950x has been reduced to a one-trick pony on desktop, and even there, the 12900k is a very close second and the better choice as the all-rounder, top-performer chip to get.

all CAD and Adobe apps are ST or very lighty threaded. So you just posted the apps where ADL specially shines. Only a very few number of those tests you posted are really MT, and in that regard, 5950x shines and wins the majority of them (CB is basically the only exception at stock, aka, 241w vs 105w, because if you use PBO, 5950X wins there too). So 5950X not only wins in MT tasks, but reachs that consuming a lot less power than 12900K.

Hulk

Diamond Member

all CAD and Adobe apps are ST or very lighty threaded. So you just posted the apps where ADL specially shines. Only a very few number of those tests you posted are really MT, and in that regard, 5950x shines and wins the majority of them (CB is basically the only exception at stock, aka, 241w vs 105w, because if you use PBO, 5950X wins there too). So 5950X not only wins in MT tasks, but reachs that consuming a lot less power than 12900K.

Seems like most of the apps that scale nearly linearly with multithreading are benchmarks. This makes sense actually because if you are writing code for a benchmark you are going to start out with the thought that it will be perfectly parallel and then you can adjust the task it is doing to that work flow.

On the other hand when you are programming an actual application you start out with what you are trying to accomplish (real world tasks) and then try to make it as parallel as possible. Unfortunately MT apps are not where we would like them and ST performance is still very important hence the good performance of Alder Lake with actual applications.

That's why Alder Lake can compete with Zen 3 on a per core basis. While the Zen 3 cores are still amazing, Golden Cove are just a bit more performant and when you add to that the clockspeed advantage of GC you see ADL doing well in ST heavy apps.

This is why I've been writing that there is some nuance in selecting the "best" CPU for your work/play flow when it comes to ADL and Zen 3. They both have strengths and weaknesses.

And honestly you can't go wrong either way.

Zen 3 is still a marvel. I remember reading the initial Anandtech review and thinking to myself "AMD has finally done it! This is their Conroe." A beautiful core, a beautiful process, and a perfectly logical product stack with 6, 8, 12, and 16 cores, each with higher single core speeds. It was and is a perfect product release.

Intel was seriously behind in the game. But they were clever. They found tiny holes in the Zen 3 product stack and went after them. Go for ST performance with architecture AND frequency, it's gonna hurt in power but we'll make up some lack of core count with smaller efficient cores. All of this had to be done in the confines of the process technology available. They did well.

AMD will be responding of course. Besides 3D cache I can see them reconfiguring things a bit to push clocks on perhaps 4 or 6 cores to increase ST performance as one idea to compete better with ADL on those apps. Intel will respond ... and so on.

This is great. I love it. We have two kick ass designs to discuss, but more importantly to actually use on a day-to-day basis. It's fun around here again.

tamz_msc

Diamond Member

Looks like a new BIOS update allows for DDR4 on Alder Lake to work at much higher frequencies than before in Gear 1 mode.

And the gaming results are mighty impressive; DDR4 dominates in some tests - only Troy Total War still favors DDR5 by a significant margin, so the utility of DDR5 for gaming is not yet realized at present.

Shadow of the Tomb Raider:

Starcraft II:

Watch Dogs Legion:

Troy A Total War Saga:

Cyberpunk 2077:

Far Cry 6:

Warzone:

And the gaming results are mighty impressive; DDR4 dominates in some tests - only Troy Total War still favors DDR5 by a significant margin, so the utility of DDR5 for gaming is not yet realized at present.

Shadow of the Tomb Raider:

Starcraft II:

Watch Dogs Legion:

Troy A Total War Saga:

Cyberpunk 2077:

Far Cry 6:

Warzone:

VirtualLarry

No Lifer

YT video with productivity and gaming benchmarks of the 12400(F) ES CPU.

In gaming, it beats the 11900K!! Also close to or beats the Ryzen R5 5600X.

igor_kavinski

Lifer

You know what would be really crazy? AMD playing fire with fire and unlocking more performance headroom by going toe to toe with i9-12900K's power limit of 241W. That would level the playing field. If that comes to pass, a lot of people are gonna go, "UGH! Not you too, AMD!" but the anti-environmentalist gamers and miners will rejoice and do their part gulping up all available supply of AMD's own power hog and lend a helping hand to destroy our climate 😀 Space habitats are the future anyway. We will destroy Earth and rebuild it from space later. That's the human mantra. Destroy first, rebuild later.AMD will be responding of course. Besides 3D cache I can see them reconfiguring things a bit to push clocks on perhaps 4 or 6 cores to increase ST performance as one idea to compete better with ADL on those apps. Intel will respond ... and so on.

Last edited:

igor_kavinski

Lifer

Intel Core i9-12900K Review: Let's Call It a Comeback | Digital Trends

I'm not sure if this has something to do with better mobo design by MSI, but DDR5 in this review is posting better scores, including breaking the 2000 barrier in Geekbench ST. Could be because DDR5-4800 has lower latency than either 5200 or 6000.

I'm not sure if this has something to do with better mobo design by MSI, but DDR5 in this review is posting better scores, including breaking the 2000 barrier in Geekbench ST. Could be because DDR5-4800 has lower latency than either 5200 or 6000.

Hulk

Diamond Member

You know what would be really crazy? AMD playing fire with fire and unlocking more performance headroom by going toe to toe with i9-12900K's power limit of 241W. That would level the playing field. If that comes to pass, a lot of people are gonna go, "UGH! Not you too, AMD!" but the anti-environmentalist gamers and miners will rejoice and do their part gulping up all available supply of AMD's own power hog and lend a helping hand to destroy our climate 😀 Space habitats are the future anyway. We will destroy Earth and rebuild it from space later. That's the human mantra. Destroy first, rebuild later.

Yes. Actually that is what I was getting at when I wrote about AMD possibly pumping up the clocks of 4 or 6 cores. Let me explain further.

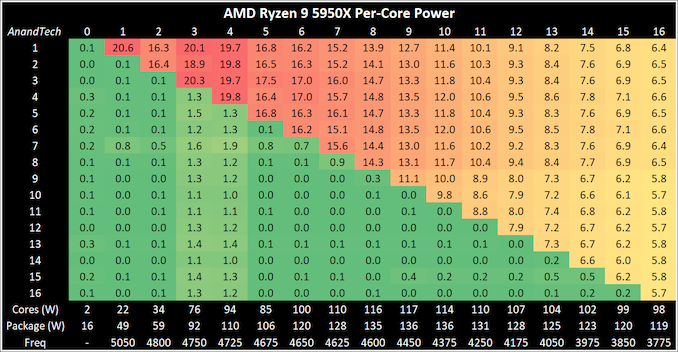

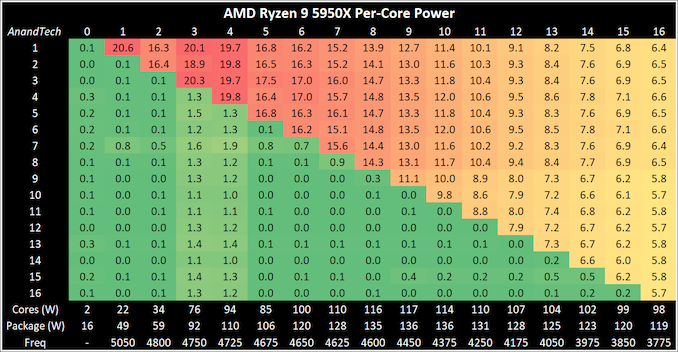

AMD could in fact "simulate" the Big/Little concept with Zen 3. Take the 5950X. If the Thread Director can be used by AMD to "figure out" that an app is really only using 6 cores then clock those 6 cores up as high as possible while clocking down the rest of the cores, performance would increase and power might not go through the roof.

Wouldn't it be a hoot if Intel/Microsoft's Thread Director turned out to be an ace up the sleeve for AMD? They already have the silicon to make it happen, it's a software problem now.

igor_kavinski

Lifer

Umm..pretty sure that Intel Thread Director is a silicon solution. Microsoft's scheduler is designed to take hints from it but it still has the final say on what it can do. The ITD cannot force Windows to run a thread on a particular core. It can only make suggestions. AMD might be preparing their own Thread Director and we might see it in Zen 4 but sadly, Zen 3D will have to do without it. But anything's possible. Who knows? AMD has surprised us (and Ian especially) before.Yes. Actually that is what I was getting at when I wrote about AMD possibly pumping up the clocks of 4 or 6 cores. Let me explain further.

AMD could in fact "simulate" the Big/Little concept with Zen 3. Take the 5950X. If the Thread Director can be used by AMD to "figure out" that an app is really only using 6 cores then clock those 6 cores up as high as possible while clocking down the rest of the cores, performance would increase and power might not go through the roof.

Wouldn't it be a hoot if Intel/Microsoft's Thread Director turned out to be an ace up the sleeve for AMD? They already have the silicon to make it happen, it's a software problem now.

igor_kavinski

Lifer

This is an ingenious idea by the way and it doesn't even need a silicon counterpart. All an application developer has to do is find out how many max cores his/her application can use effectively and then feed that value at application launch into the Windows scheduler. Windows scheduler can then communicate this value to AMD Ryzen Master which can then proceed to optimize the performance/power efficiency of the cores. It can be a completely software-only solution....to "figure out" that an app is really only using 6 cores then clock those 6 cores up as high as possible while clocking down the rest of the cores, performance would increase and power might not go through the roof.

Hulk

Diamond Member

This is dangerous but I'm going to post it. Here are my observations of ADL and Zen 3 from what I have learned so far. Please feel free to let me know how I can change the wording here to make it more acceptable to all. The point is to try and find some common ground/facts that we can all agree on as we continue to discuss ADL and Zen 3.

Overall Golden Cove has a slightly higher IPC than Zen 3. It varies by application from only 1% in Cinebench R23 to ?% in ?.

The Golden Cove cores provide additional statistically significant single thread compute over Zen 3 due to minor IPC advantage (see point 1) AND additional frequency. Golden Cove pays a price for this added performance in terms of power usage (efficiency) by pushing frequency into the nonlinear portion of the voltage vs. frequency plot.

In multi-threaded applications that scale linearly (or nearly so) with the number of cores, assuming comparable micro-architecture and process technology, more cores at lower frequency will be more efficient than less cores at higher frequency.

In an effort to increase multi-threaded performance and efficiency while optimizing die space Intel added Gracemont cores to Alder Lake. The primary reason for the Gracemont cores is to provide as much multi-threaded performance as possible in the die area available and power they consume.

In applications that stress less than 8 cores the 12900K will generally perform better than the 5950X. At roughly equal performance levels for these types of applications power usage will be approximately the same.

In applications that stress 16 or more cores the 5950X will generally perform better than the 12900K and be more efficient. See point 3.

The “balance of power” between the 5950X and the 12900K will vary with applications that require between 8 and 16 cores.

As the programming of multi-threaded applications becomes more efficient the path to better performance will be increasing the number of cores. AMD is already poised for this as they have parts extending to 64 cores with high core count parts coming. Intel can make a gradual transition from ST to MT performance optimization by using additional die area from process shrinks to maintain the number of big cores while increasing the number of small cores and possible eventually starting to decrease the number of small cores.

Alder Lake and Zen 3 Overview

Overall Golden Cove has a slightly higher IPC than Zen 3. It varies by application from only 1% in Cinebench R23 to ?% in ?.

The Golden Cove cores provide additional statistically significant single thread compute over Zen 3 due to minor IPC advantage (see point 1) AND additional frequency. Golden Cove pays a price for this added performance in terms of power usage (efficiency) by pushing frequency into the nonlinear portion of the voltage vs. frequency plot.

In multi-threaded applications that scale linearly (or nearly so) with the number of cores, assuming comparable micro-architecture and process technology, more cores at lower frequency will be more efficient than less cores at higher frequency.

In an effort to increase multi-threaded performance and efficiency while optimizing die space Intel added Gracemont cores to Alder Lake. The primary reason for the Gracemont cores is to provide as much multi-threaded performance as possible in the die area available and power they consume.

In applications that stress less than 8 cores the 12900K will generally perform better than the 5950X. At roughly equal performance levels for these types of applications power usage will be approximately the same.

In applications that stress 16 or more cores the 5950X will generally perform better than the 12900K and be more efficient. See point 3.

The “balance of power” between the 5950X and the 12900K will vary with applications that require between 8 and 16 cores.

As the programming of multi-threaded applications becomes more efficient the path to better performance will be increasing the number of cores. AMD is already poised for this as they have parts extending to 64 cores with high core count parts coming. Intel can make a gradual transition from ST to MT performance optimization by using additional die area from process shrinks to maintain the number of big cores while increasing the number of small cores and possible eventually starting to decrease the number of small cores.

TheELF

Diamond Member

That is a very basic functionality of turbo and has been used for years and years now by both intel and amd.AMD could in fact "simulate" the Big/Little concept with Zen 3. Take the 5950X. If the Thread Director can be used by AMD to "figure out" that an app is really only using 6 cores then clock those 6 cores up as high as possible while clocking down the rest of the cores, performance would increase and power might not go through the roof.

Ryzen master even tells you which cores are "the best" reaching highest clocks with the least Vcore.

AnandTech Forums: Technology, Hardware, Software, and Deals

Seeking answers? Join the AnandTech community: where nearly half-a-million members share solutions and discuss the latest tech.

www.anandtech.com

Markfw

Moderator Emeritus, Elite Member

Pretty good IMO. The only thing I am not sure, is that you say the Alder lake will be similar power usage or lower at 8 cores or less. Since they start out so much lower overall, I would think Zen would win at all byt very low core count tasks , where the IO chips overhead comes in. At most anything over 8 cores, 5950x should be better in most applications.This is dangerous but I'm going to post it. Here are my observations of ADL and Zen 3 from what I have learned so far. Please feel free to let me know how I can change the wording here to make it more acceptable to all. The point is to try and find some common ground/facts that we can all agree on as we continue to discuss ADL and Zen 3.

Alder Lake and Zen 3 Overview

Overall Golden Cove has a slightly higher IPC than Zen 3. It varies by application from only 1% in Cinebench R23 to ?% in ?.

The Golden Cove cores provide additional statistically significant single thread compute over Zen 3 due to minor IPC advantage (see point 1) AND additional frequency. Golden Cove pays a price for this added performance in terms of power usage (efficiency) by pushing frequency into the nonlinear portion of the voltage vs. frequency plot.

In multi-threaded applications that scale linearly (or nearly so) with the number of cores, assuming comparable micro-architecture and process technology, more cores at lower frequency will be more efficient than less cores at higher frequency.

In an effort to increase multi-threaded performance and efficiency while optimizing die space Intel added Gracemont cores to Alder Lake. The primary reason for the Gracemont cores is to provide as much multi-threaded performance as possible in the die area available and power they consume.

In applications that stress less than 8 cores the 12900K will generally perform better than the 5950X. At roughly equal performance levels for these types of applications power usage will be approximately the same.

In applications that stress 16 or more cores the 5950X will generally perform better than the 12900K and be more efficient. See point 3.

The “balance of power” between the 5950X and the 12900K will vary with applications that require between 8 and 16 cores.

As the programming of multi-threaded applications becomes more efficient the path to better performance will be increasing the number of cores. AMD is already poised for this as they have parts extending to 64 cores with high core count parts coming. Intel can make a gradual transition from ST to MT performance optimization by using additional die area from process shrinks to maintain the number of big cores while increasing the number of small cores and possible eventually starting to decrease the number of small cores.

NOTE. The 12600k and the 12700k are a different case. MUCH more power efficient than the 12900k at any usage.

I'm not sure if this has something to do with better mobo design by MSI, but DDR5 in this review is posting better scores, including breaking the 2000 barrier in Geekbench ST. Could be because DDR5-4800 has lower latency than either 5200 or 6000.

It is cause of using basic grade DDR4 3200 with unknown timings and no tuning. A sort of config that prefers a DDR5 setup that gives 50% of bandwidth advantage for equally horrible latencies.

ADL is a case of very strong core held back by horrible memory subsystem, one that is hilariously slower than AMD's IOD solution when coupled with the same speed/latency DRAM.

No wonder that next gen with same P core will turn to something Intel calls "gaming cache optimizations".

Hulk

Diamond Member

That is a very basic functionality of turbo and has been used for years and years now by both intel and amd.

Ryzen master even tells you which cores are "the best" reaching highest clocks with the least Vcore.

AnandTech Forums: Technology, Hardware, Software, and Deals

Seeking answers? Join the AnandTech community: where nearly half-a-million members share solutions and discuss the latest tech.www.anandtech.com

Yes but how fine grained is the decision making process? If 2 cores are completely floored, 4 heavily loaded, 2 moderately loaded, and 8 lightly loaded can Ryzen Master adjust clocks appropriately or will it just run all 16 at the same frequency since they are all effectively doing some work?

TheELF

Diamond Member

That's the best you will get without a hardware thread director inside the cpu that can actually tell the OS what the code does and can help it decide if it's high priority or not.Yes but how fine grained is the decision making process? If 2 cores are completely floored, 4 heavily loaded, 2 moderately loaded, and 8 lightly loaded can Ryzen Master adjust clocks appropriately or will it just run all 16 at the same frequency since they are all effectively doing some work?

igor_kavinski

Lifer

So there's a good chance that Raptor Lake may have a large L4 cache aka Crystal Well, to hide memory latencies?ADL is a case of very strong core held back by horrible memory subsystem, one that is hilariously slower than AMD's IOD solution when coupled with the same speed/latency DRAM.

Asterox

Golden Member

YT video with productivity and gaming benchmarks of the 12400(F) ES CPU.

In gaming, it beats the 11900K!! Also close to or beats the Ryzen R5 5600X.

Old news, this is just bench data from French comptoir-hardware.com.

Question - Alder Lake - Official Thread

Page 28 - Seeking answers? Join the AnandTech community: where nearly half-a-million members share solutions and discuss the latest tech.

forums.anandtech.com

DrMrLordX

Lifer

Seems like most of the apps that scale nearly linearly with multithreading are benchmarks. This makes sense actually because if you are writing code for a benchmark you are going to start out with the thought that it will be perfectly parallel and then you can adjust the task it is doing to that work flow.

That's not necessarily a very good benchmark though (and the term you're likely looking for here is: synthetic benchmark). Actually useful benchmarking entails test runs with real-world applications people use every day to get work done. There are a few such applications that are embarrassingly-parallel, such as Blender.

You know what would be really crazy? AMD playing fire with fire and unlocking more performance headroom by going toe to toe with i9-12900K's power limit of 241W.

Not really. Chips like the 5900X and 5950X wouldn't scale all that well with additional power. It's so hard to cool them with air or water.

coercitiv

Diamond Member

Let's start this week with a very positive spin for some enthusiasts: one great thing about Intel's decision to go ham on power draw over the last 5 years has resulted in the best thermal conductivity they could come up with between the die and IHS.

We came a very very long way from the poor TIM used starting with Ivy Bridge: back to solder in Coffee Lake refresh, and them incremental improvements to die height and packaging to maximize thermal conductivity. The result is, ironically, the best configuration for an enthusiast looking to build a very silent system, as all this change in thermal resistance at the die interface has a major influence on the cooling efficiency of passive and semi-passive cooling.

Every time my CPU fan spins up to the audible threshold I am reminded I was just 1 generation away from Intel correcting their path. Had it been a CFL refresh chip, the fan would have stayed silent.

We came a very very long way from the poor TIM used starting with Ivy Bridge: back to solder in Coffee Lake refresh, and them incremental improvements to die height and packaging to maximize thermal conductivity. The result is, ironically, the best configuration for an enthusiast looking to build a very silent system, as all this change in thermal resistance at the die interface has a major influence on the cooling efficiency of passive and semi-passive cooling.

Every time my CPU fan spins up to the audible threshold I am reminded I was just 1 generation away from Intel correcting their path. Had it been a CFL refresh chip, the fan would have stayed silent.

Hulk

Diamond Member

Appreciate if you can run with only P-cores and AVX-512. Curious if that scores higher than stock setting.

As it turns out I was running the initial BIOS release. I updated the BIOS and after disabling the E cores AVX512 became available.

193.05 seconds with AVX512 on P cores only. 11% improvement with AVX512 and only about 20 seconds slower than P+E.

TRENDING THREADS

-

Discussion Zen 5 Speculation (EPYC Turin and Strix Point/Granite Ridge - Ryzen 9000)

- Started by DisEnchantment

- Replies: 25K

-

Discussion Intel Meteor, Arrow, Lunar & Panther Lakes + WCL Discussion Threads

- Started by Tigerick

- Replies: 25K

-

Discussion Intel current and future Lakes & Rapids thread

- Started by TheF34RChannel

- Replies: 24K

-

-