I am not even sure if Threadripper is right product for 3D cache in the world of limited wafers.

This might be something to consider, if Threadripper had any volume, like, say the old Intel HEDT platform. But since Threadripper has miniscule volume, the wafers needed to add V-Cache for Threadripper are likewise miniscule.

HEDT is niche within niche already and i think there are two main "volume" uses for such chips:

1) Rendering - at least Cinebench does not scale with L3 cache size once it has enough ot it and we are long past that point. Probably similar story with other renderers that are still stuck on CPU and not using GPUs for reasons?

2) IO heavy setups with GPUs or storage, these don't care about caches either

Other than that - for example code compiler style of usage, remains to be seen how much it is helped by increased L3, it is usually thread count affair as long as memory subsystem is competent, and ZEN3 already has one in place.

The generic workstation for modelling, CAD and so on might benefit somewhat, as it's usually all about several strong threads and GPU acceleration there, but 32MB of L3 is already plenty good

I think AMD product positioning misfired with Threadripper. They had a perfect opportunity to claim 2 different market niches with 2 different products:

- workstation

- HEDT

AMD already had 2 platforms perfectly positioned for these 2 niches:

- 8 memory channel for workstation

- 4 memory channel for HEDT

And they also have to brand names, that would seemingly fit perfectly these 2 different market segments:

- Threadripper

- Threadripper Pro

But where AMD dropped the ball is SKUs that would target these 2 segments. The Threadripper SKU targeting is not only incomprehensible, it is counter intuitive.

For example, Threaddripper Pro, that would be more suited for Workstation (8 channel) segment, starts from 12 and 16 cores. But the vanilla Threadripper, that would be well suited for HEDT starts from 24 cores and up.

Desktop and servers is where 3D cache can help the most and even on desktop AMD is touting the gaming as the one where the benefits are largest: hard to escape the fact that to render each frame game has to go over huge working set of data, communicate with DirectX or Vulcan runtime, that in turn communicates with GPU drivers that chew that freshly generated data and render it on screen. So ton of benefits can be had here by using enlarged L3 for communication and avoiding going to memory.

But even in gaming there are limits, just like AMD during ZEN days was fond of GPU bottlenecked games, 3D cache will take "competitive" games with absurd FPS rates to really shine, while giving little benefit to the "averages" when GPU bottlenecked. Frankly it will help the most in minimums and consistency, that is area that AMD ironically overlooked over Zen/Zen2 era and will now need to tout hard.

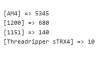

There are some nice opportunities on desktop, and AMD could also play high end of this segment with Threadripper with 3D cache, with non-Pro, 4 channel platform. Perhaps starting from as little as a single CCD and more layers of V-Cache at ~$500 and up from there. What made Intel HEDT successful what generated most of the volume for the platform were not the $1,000 CPUs but the $500 CPUs.

Just from knowing what I would ideally want in my upgrade from Intel HEDT to AMD HEDT - the chances are that AMD will not sell it and will miss the boat again.

If the Threadripper present is a good predictor of Threadripper future, chances are that AMD will have all the components I want, but will misconfigure them to a Frankenstein configuration I don't want.