I cannot tell you exactly, how intense matrix math is in game engines. But it is for certain, that matrices get used everywhere in games (you can google that if you want). And today this means, that you make N-times vector * vector math instead of 1-time matrix * vector. For some part this split into multiple vectors is useful, because it allows for easy parallelization on wide SIMD units of a GPU. But you can do that with matrices as well, because you have millions of pixels anyways.

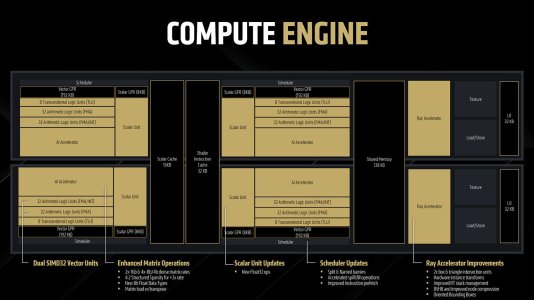

I would suspect, that the cooperative vector API greatly reduce the transition overhead between matrix cores and other parts of a CU. And in the end, everything uses the same registers and caches of a CU or SM. So the main thing you need to care about is data alignment (vectors vs. matrices) that you do not need to shuffle around your data when switching between vectors and matrices. How big the actual benefits will be, have to be seen. I hope we see some talks and presentations about cooperative vectors from AMD, Nvidia and game developers.

For me, there is another reason for matrices:

Optimize performance in general. Game developers used vector math for ages. Now they could reshape their algorithms to do direct matrix math. Will it be faster? It depends on the use case. But I could very well imagine, that it would allow developers to push further. As you said, with matrix operations you optimize for bandwidth and power. Both is scarce on GPUs if you want to get optimal performance. Will that take some effort and time? Sure.

I do not see it happening too soon, earliest with the next console cycle because those will support WMMA acceleration. If you want to squeeze the maximum out of a console, optimize your code and increase the utilization of the available hardware units. Most image filters kernels (e.g. Lanczos) use matrices (e.g. postprocessing in games), vector*matrix for orientation & transformation of things, dot-products for geometric stuff and so on. If the data is aligned right, you can put that into vectors or matrices, the result is the same.

I would suspect, that the cooperative vector API greatly reduce the transition overhead between matrix cores and other parts of a CU. And in the end, everything uses the same registers and caches of a CU or SM. So the main thing you need to care about is data alignment (vectors vs. matrices) that you do not need to shuffle around your data when switching between vectors and matrices. How big the actual benefits will be, have to be seen. I hope we see some talks and presentations about cooperative vectors from AMD, Nvidia and game developers.

For me, there is another reason for matrices:

Optimize performance in general. Game developers used vector math for ages. Now they could reshape their algorithms to do direct matrix math. Will it be faster? It depends on the use case. But I could very well imagine, that it would allow developers to push further. As you said, with matrix operations you optimize for bandwidth and power. Both is scarce on GPUs if you want to get optimal performance. Will that take some effort and time? Sure.

I do not see it happening too soon, earliest with the next console cycle because those will support WMMA acceleration. If you want to squeeze the maximum out of a console, optimize your code and increase the utilization of the available hardware units. Most image filters kernels (e.g. Lanczos) use matrices (e.g. postprocessing in games), vector*matrix for orientation & transformation of things, dot-products for geometric stuff and so on. If the data is aligned right, you can put that into vectors or matrices, the result is the same.