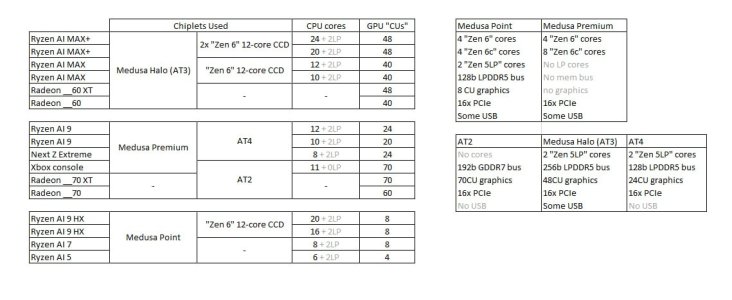

AMD could be trolling NVidia on low end with big LPDDR5 memory sizes.

What I wonder though, why not doe the same throughout the stack?

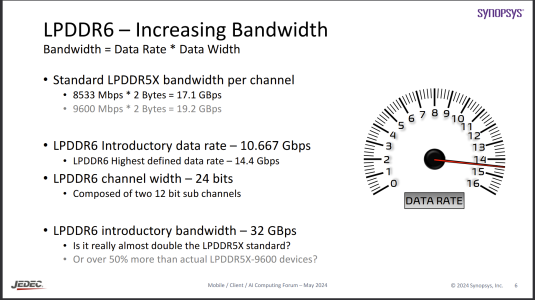

If NVidia can go up to 512 bit memory bus (8 channels) why not go to 6 LPDDR6 channels with high end card, which would be 576 bits?

Because then, if the biggest LPDDR5 memory chip is 64 GB, the high end professional / AI card could have 384 GB, which would be maximum trolling.

Or maybe split high end gaming to use GDDR7 and high end professional / AI with LPDDR6.

But, it's also good to keep in mind that NVidia is also doing a lot of work with LPDDR across the product stack, so AMD may not have a monopoly here.