DisEnchantment

Golden Member

Speculate at will

Last edited:

Wait. You’re telling me my out-of-left-field guess had merit?!I mean I didn't actually outright say that it was an LP island on here... but yeah, I guess the secret's out? I really don't want to be the one to spill the beans on some of the details of it though, so the only thing I'm going to say is the comparison to A10 fusion was intentional. Especially wrt scheduling.

cc @Gideon because I see you just asked in the other thread.

Just a total dart throw, but one thing it would be nice to see AMD do is to match Intel in reducing their idle power consumption via the use of a low power core. I recall there being an AMD patent a ways back where they had the cache of a big core be shared with a small core or something to that effect where in essence the workload could be passed between the cores without much penalty. If Zen 6’s IOD uses N4X then you could make that small core pretty power efficient by using those uLVT transistors and shutting down the compute die. Plus, the use of Infinity Link or whatever AMD calls it to connect the compute die to the IOD may allow for the small core approach to work. Given that Adroc hinted that Zen 6 desktop is more mobile-like than ever, this idea is not too far fetched in my opinion.

Edit: found the article.

AMD patents a task transition method between BIG and LITTLE processors - VideoCardz.com

AMD “big.LITTLE” aka heterogeneous computing in Ryzen 8000 series The next decade will no longer be dictated by the number of cores, but rather the processor’s fabrication node, packaging method, and power effciency. A big role will also be played by heterogeneous architectures. Later this year...videocardz.com

Yeah, that's where I went back to to follow the full trail.Wait. You’re telling me my out-of-left-field guess had merit?!

What motivation would Microsoft have to butt in here? Security? Why do they care what cores their software runs on? If someone replies, please avoid unnecessary Microsoft bashing.You got the additional information on your own already by now, but just for clarification again: That's wasn't true during the Bulldozer years. There were those infamous cores called construction cores (Bulldozer Piledriver, Steamroller, Excavator) that made AMD uncompetitive during those years, and the low power cat cores (Bobcat, Jaguar, Puma) that at least kept AMD in the games consoles business if nothing else.

That's with OS visible cores where the scheduler may be too stupid avoiding moving tasks to incompatible cores.

There had been an interesting AMD patent that talks about very small cores just implementing fast basic instructions (essentially only for I/O without actual computing) that otherwise cause an exception with the task then being moved to the full core, all of that being completely hidden from the OS. (I'd have to search for the patent, but we discussed it several times in the past.)

The issue about that is that I recall Microsoft recently making it a rule that it's no longer allowed to hide such cores from Windows so such hardware if realizable may end up not being used under Windows anyway.

It's Zen5 derivative but I dunno how lobotomized it actually is.- They'll be Cat like cores that aren't "proper Zen 5".

We have been totally jebaited, he didn't know about it at all.crikey, the chief e-beggar leaked the funny bit out.

It's Zen5 derivative but I dunno how lobotomized it actually is.

why dropped them on their heads as childrenI think MLID thinks the LP is for Strix Halo handheld model rather than a Low Power Island for Z5 lol

Also, Phawx thinks a 8C + 40CU is ideal for a handheld...🙃

oh god time to delete my poast.We have been totally jebaited, he didn't know anything at all.

Maybe he just wants to start an "InsulatedGlovesGaming" channel.Also, Phawx thinks a 8C + 40CU is ideal for a handheld...🙃

I mentioned it in this thread before actually:There had been an interesting AMD patent that talks about very small cores just implementing fast basic instructions (essentially only for I/O without actual computing) that otherwise cause an exception with the task then being moved to the full core, all of that being completely hidden from the OS. (I'd have to search for the patent, but we discussed it several times in the past.)

@adroc_thurston previously mentioned in this thread that Microsoft now mandates that all cores be visible to the OS:The issue about that is that I recall Microsoft recently making it a rule that it's no longer allowed to hide such cores from Windows so such hardware if realizable may end up not being used under Windows anyway.

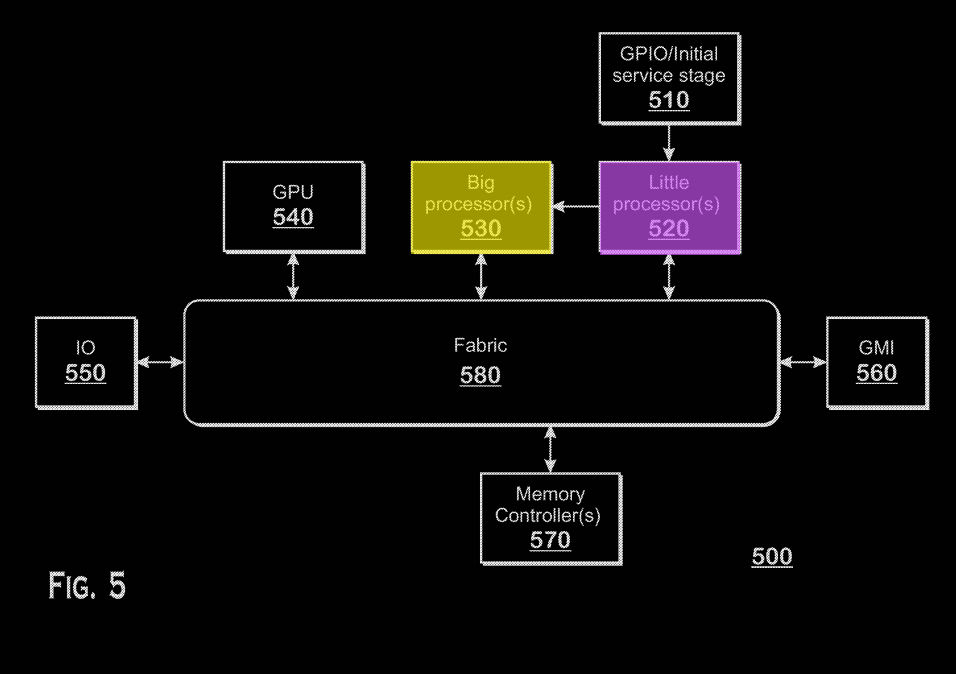

So that would mean something like:

new info about zen5 apu

I'm not sure if monolithic Strix and Kraken will feature Z5 LP cores. They're probably for Halo only. I'm expecting a quad-core complex for Z5 LP on Halo.So that would mean something like:

Z5x4, Z5cx8, Z5LPx4?

Especially if you leave off Strix Point, that IIRC is 4xZ5, 8xZ5c?

They are for Halo only, or so Adroc said.I'm not sure if monolithic Strix and Kraken will feature Z5 LP cores. They're probably for Halo only.

Yes, SP is 4x Z5 + 8Z5C. KRK is either 4P + 4E or binned 2P + 4E.

From an engineering and TTM standpoint, this does make more sense than building off a dedicated new Cat core. Z5/Zen cores is ISA compatible, power efficient at lower levels and very small already. So it's the perfect choice.crikey, the chief e-beggar leaked the funny bit out.

It's Zen5 derivative but I dunno how lobotomized it actually is.

Oh, you misunderstood me. Kraken is replacing PHX/HWK in mainstream laptops (<$999/$800). Its the same strategy as Strix Point: Mixing Zen 5 Classic cores with Zen 5 Dense cores.Dunno if KRK will have an advanced packaging like this for a low end part, I doubt they'll put LP cores there first. Halo seems to be really an early peek into Zen 6's packaging and lineup differentiations.

They aren't.and very small already.

Weren't Z4 around ~4mm² and Z4D ~3mm? Z5 is probably bigger, but when you compare to Intel P...They aren't.

Question is, what survived the lobotomy.

When the forum will start taking time to load, it's the bots rushing to copypaste the thread all at once.Wouldn’t be surprised. Sleuths gonna sleuth to keep those clickbait articles coming.

No one said it has to be a Zen 5 derivative, right? Wouldn’t a Zen 4 core also work? As long as it has the same ISA and can more or less execute the same instructions, even if it’s at half rate, it should be fine, no? Cutting the FP block is generally a low hanging fruit if you want to reduce the core size. It doesn’t mean it cant support AVX-512 still.They aren't.

Question is, what survived the lobotomy.

I'm not sure if monolithic Strix and Kraken will feature Z5 LP cores. They're probably for Halo only. I'm expecting a quad-core complex for Z5 LP on Halo.

Yes, SP is 4x Z5 + 8Z5C. KRK is either 4P + 4E or binned 2P + 4E.

The cats were built by a tiny team, that managed to massively outpetform expectations.AMD developed the Cat lineage until before Zen launch. By then, the market for these type of x86 cores was becoming smaller and smaller due to Arm competition, failure of x86 at Mobile markets and AMD difficulties in general.

Wait, the Austin M series team was derived from the AMD Cat team? Huh, that's actually surprising. Had no idea, thanks for sharing.The cats were built by a tiny team, that managed to massively outpetform expectations.

The reason cat core development ended was not about the market, it was that someone (iirc Samsung? Not sure and I don't have time to check it) poached the entire team whole from AMD. This was before the Zen success and when AMD had money issues.

Think Intel like. A P core, an E core and a LP Core Complex Island at the SoC.If I am understanding what is being discussed correctly, it is not a core at all - just like a filter on top of regular Zen 5 cores that can carry out a subset of instructions in a power efficient manner without waking up the full core.

If this is the case, why would this be exclusive to Halo? Perhaps because Zen 5C doesn't really benefit?