- Mar 3, 2017

- 1,779

- 6,798

- 136

Ughhh depends on the workload.the RAM, memory and latency is the bigger bottleneck.

Aye. I assume it's a 4 - 6 Core Island to avoid Intel MTL situation where the LPE are too few to even run anything while the Compute Die idle.LP Core "island" meaning...there's a part of the die that's specifically designed for low power usage and shuts off the rest of the die on idle?

Very interesting, but the latter part is a bold assumption.Aye. I assume it's a 4 - 6 Core Island to avoid Intel MTL situation where the LPE are too few to even run anything while the Compute Die idle.

And I don't think these are "Zen 5" cores proper. I assume this is a specifically designed new Cat like core for very low power, unlike LPE which are rehashed E cores. Scheduling would be a mess, but maybe there are some ways to work around it?

I mean I didn't actually outright say that it was an LP island on here... but yeah, I guess the secret's out? I really don't want to be the one to spill the beans on some of the details of it though, so the only thing I'm going to say is the comparison to A10 fusion was intentional. Especially wrt scheduling.Credits to Uzzi

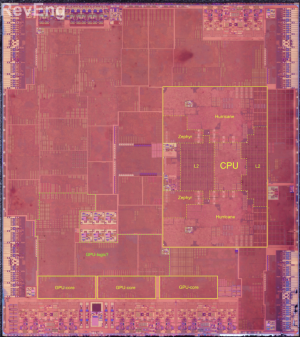

Already being discussed on another thread, but mlid leaked the one of the reasons why Adroc thinks Halo is the most cool part of Zen 5 line-up: Strix Halo features LP Core island.

This is what Branch_Suggestion and Uzzi alluded at last week.

Strix Halo is basically a preview of Zen 6: Advanced Packaging + Bigger SoC die with IGP and LP Island.

It would be wonderful to see a a cat-core derivate solution!Aye. I assume it's a 4 - 6 Core Island to avoid Intel MTL situation where the LPE are too few to even run anything while the Compute Die idle.

And I don't think these are "Zen 5" cores proper. I assume this is a specifically designed new Cat like core for very low power, unlike LPE which are rehashed E cores. Scheduling would be a mess, but maybe there are some ways to work around it?

cc @Gideon because I see you just asked in the other thread.

You had said it was related to the A10 example and the last week discussions about AMD patents. Also, there is a old image about AMD roadmap (I think it's from MLID too?) that also features "low power Core options" for Zen 5. So I kind connected the dots.I mean I didn't actually outright say that it was an LP island on here... but yeah,

Isn't that basically Phoenix 2?Yeah i was just thinking in the other thread, could it be connected to this patent:

AMD Files Patent for its Own x86 Hybrid big.LITTLE Processor

AMD is innovating its own x86 hybrid processor technology formulated along the Arm big.LITTLE hybrid CPU core topology that inspired Hybrid processors by Intel. Under this, the processor has two kinds of CPU cores with very different performance/Watt bands—one kind focuses on performance and...www.techpowerup.com

Pretty sure there's a Displayport feature that does something like refresh a display without actually requiring a continuous signal if nothing new is being sent.Hopefully something on the igpu side as well, that could drive/refresh a single screen without powering on the full display engine (or something).

It would be wonderful to see a a cat-core derivate solution!

Is it that or did Intel do something else wrong? Ofc 2 little Cores aren't much, but they are about skylake in performance and 2 skylake Cores should be able to run a web browser. Yet the battery life of MTL is only good with deactivated WIFI. I feel like the problem is something different than pure lack of performance of those Cores.Aye. I assume it's a 4 - 6 Core Island to avoid Intel MTL situation where the LPE are too few to even run anything while the Compute Die idle.

Lets just say there's a very good reason why Intel are moving on to 4 LP-E cores so quickly (Lunar Lake, Panther Lake etc).Is it that or did Intel do something else wrong? Ofc 2 little Cores aren't much, but they are about skylake in performance and 2 skylake Cores should be able to run a web browser. Yet the battery life of MTL is only good with deactivated WIFI. I feel like the problem is something different than pure lack of performance of those Cores.

6nm? I'm pretty sure the rumor is that CCDs are N4X while SoC is N3E, no?

For Strix Halo I mean

I hope they go for something much more purpose built, for instance, compared to the likes of QCM that would be extremely overkill.It would be wonderful to see a a cat-core derivate solution!

It's a shorthand to Bobcat. Bobcat was a line of small, ultra low power cores that AMD developed for the then nascent and rising Tablet/Netbook markets, with focus on 1 - 10W designs. The most famous implementation of Bobcat line of cores was on the consoles PS4 and Xbox One.What's a cat core?

I'm not too knowledgeable about A10. Neither my little research was anything deep. But what I could find was:so the only thing I'm going to say is the comparison to A10 fusion was intentional. Especially wrt scheduling.

One thing Apple has emphasized in talking about the A10 is that their design uses a custom designed performance controller to manage the CPU cores and migrate tasks between them.

It was not only Bobcat in that line of products, there were also the Puma and Jaguar, which were all... cats. So all these cores were called the AMD "Cats" family.It's a shorthand to Bobcat. Bobcat was a line of small, ultra low power cores that AMD developed for the then nascent and rising Tablet/Netbook markets, with focus on 1 - 10W designs. The most famous implementation of Bobcat line of cores was on the consoles PS4 and Xbox One.

AMD developed the Cat lineage until before Zen launch. By then, the market for these type of x86 cores was becoming smaller and smaller due to Arm competition, failure of x86 at Mobile markets and AMD difficulties in general.

So when people talk about a Cat core, they mean a new core that is focused on ultra low power like the Bobcat were.

The cores must have same instruction set architecture, otherwise AMD will end up like Intel disabling features of big core. For IO die, they can use a low power 4 core APU added with more IO paths.So, going back to AMD implementation and comparison with A10, this is what I think:

- Unlike Zephyr, they'll be located outside of the CCD, at the SoC die.

- They'll be Cat like cores that aren't "proper Zen 5".

- Unlike Intel, where they leave to Windows scheduler and Thread Director to schedule things to LPE cores accordingly (And fail most of the time), AMD will be doing a custom hardware solution, like Apple, that "bypass" the OS scheduling and force things unto the Low Power Island.

This is a very outlandish idea and I don't even know if it's feasible. Maybe some kind of firmware layer in-between or something. But the idea should be that the Low Power Island will be akin to phones always on processor and handle low power/compute tasks and idling situations while the CCDs are at a minimum power state possible, basically "shutdown".

I don't think my idea make any sense, but worth the shot🤣

You got the additional information on your own already by now, but just for clarification again: That's wasn't true during the Bulldozer years. There were those infamous cores called construction cores (Bulldozer Piledriver, Steamroller, Excavator) that made AMD uncompetitive during those years, and the low power cat cores (Bobcat, Jaguar, Puma) that at least kept AMD in the games consoles business if nothing else.AMD has been making one core, and only one core, since forever.

That's with OS visible cores where the scheduler may be too stupid avoiding moving tasks to incompatible cores.The cores must have same instruction set architecture, otherwise AMD will end up like Intel disabling features of big core. For IO die, they can use a low power 4 core APU added with more IO paths.

Yes I'm rethinking after reading all of Ghosts' posts and the patent.You got the additional information on your own already by now, but just for clarification again: That's wasn't true during the Bulldozer years. There were those infamous cores called construction cores (Bulldozer Piledriver, Steamroller, Excavator) that made AMD inconmpetitive during those years, and the low power cat cores (Bobcat, Jaguar, Puma) that at least kept AMD in the games consoles business if nothing else.