DisEnchantment

Golden Member

Speculate at will

Last edited:

Less heat != less temperature. Lower power consumption is more than offset by growth in density => more temperature. So heat dissipation does not get better, it gets worse.I am NOT an expert, at all ... ... but I tend to think about it as : the smaller node [@ iso-frequency] ... the less heat ...

nope, the smaller the node the less energy for the gate , but as the wire shrinks resistance skyrockets.I am NOT an expert, at all ... ... but I tend to think about it as : the smaller node [@ iso-frequency] ... the less heat ...

nope, the smaller the node the less energy for the gate , but as the wire shrinks resistance skyrockets.

Their predictability and consistency has actually worked so much in NV's favour.

How does 40%+ IPC sound?Is AMD going to shock the PC industry in June?

Will it be bigger than Zen3/4?

isn't 40% not ipc but core-to-core improvement?How does 40%+ IPC sound?

It matters.they're all very incremental so not really.

Someone here said that the latest beta bios with Zen 5 support was very different to previous bioses. Sounds like AMD has reorganised the code, maybe even rewritten sections and things needs to be tested so they threw in future upcoming stuff."AM5+ in 2026"

AMD may have a new platform for upcoming Ryzen CPUs — AM5+ socket and Granite Ridge CPUs listed in a microcode extraction tool

AM5+ platform could come with new features.www.tomshardware.com

Why the heck would we be seeing a patch now then?

No, only larger shrinks matter much but still.It matters.

Every little bit does.

all these people who where never hear for 180 -> 130 -> 90 -> 65 -> 32 .It matters.

Every little bit does.

Like how many small streams join to make a roaring river.

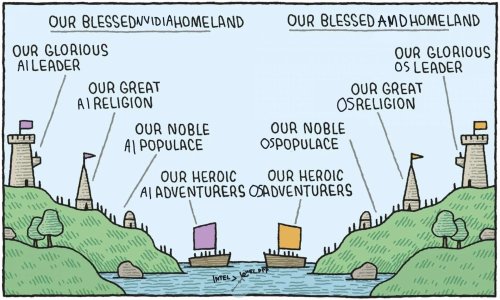

Can you stop with the spam? It's honestly garbage.View attachment 96504

Zen1 : A New Hope

Zen2 : The Return of AMD

Zen3 : The Rise of Zen

Alder Lake : Revenge of the Intel

Zen4 : The AM5 Menace

Raptor Lake : Attack of the E-cores

Zen5 : The AMD Strikes Back

Arrow Lake : The Intel Awakens

Zen6 : The Last Zen

Reddit posters aren't exactly known for quality etiquette. Forums actually have posting standards that people try to adhere to.Can you stop with the spam? It's honestly garbage.

Or not...Forums actually have posting standards that people try to adhere to.

Depends on the forum in question I suppose...Or not...

I thought it was funny! =)Depends on the forum in question I suppose...

Me too lolI thought it was funny! =)

FYI, this is actually an old sample, like several months old.

FYI, this is actually an old sample, like several months old.