DisEnchantment

Golden Member

Speculate at will

Last edited:

There are no "next-gen boards" (and why would they be called 800-series when current boards are 600-series?)According to MLID Zen 5 will arrive late because of Mainboard issues. He says that the announcement will probably be around computex with availability later...does not sound good to me. I thought april was kinda save...

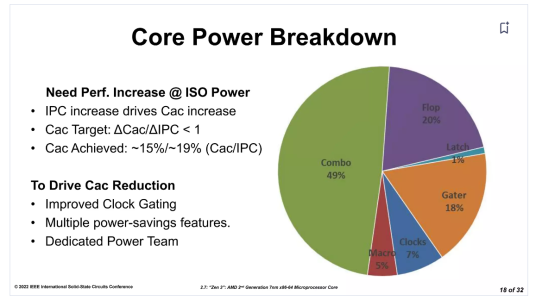

no lol, clocks aren't going anywhere.IPC is the only way companies will be able to extract performance on smaller nodes.

AMD is aiming for chunggus IPC because they have a dense core to sell where it matters. Which demands very high IPC to clap the likes of Neoverse V et al.If AMD was able to do it on N4 - its a good showcase of what is coming on smaller nodes, albeit with lower density gains than before.

Soooooooo just to clarify this 100%. You are talking HIGHER and not way LOWER or something and that's why it sounds like bs, right?That's not the real number, the real number sounds like pure bs.

It just showcases the general direction of Z5 and future AMD cores (chunggus IPC bumps to make dense a very viable option across data center in general, not just cloud in particular).

Sounds expensive.AMD is aiming for chunggus IPC because they have a dense core to sell where it matters. Which demands very high IPC to clap the likes of Neoverse V et al.

Yea.You are talking HIGHER and not way LOWER or something and that's why it sounds like bs, right?

naa.It's easy. Zen 5 has roughly 45% higher IPC than Zen 4 and can hit 5.2 GHz single core boost. That would give Zen 5 roughly 32% more overall single thread performance over Zen 4 which is where that number really comes from. Done.

Leadership isn't free.Sounds expensive.

In transistors and die size, especially.

There is no free lunch anymore. Even here, on this front.Leadership isn't free.

You've seen MI300.

But again, AMD CPU teams are very good at IPC:Cac and IPC:area metrics.

There hasn't been a free lunch on IPC front since like P6/K7 era.There is no free lunch anymore. Even here, on this front.

There’s an ancient cinememe leak from anandtech’s favorite leaker (MLID) showing a dual socket 64C Turin ES sample and the results suggest the nT uplift isn’t 40%+.It's easy. Zen 5 has roughly 45% higher IPC than Zen 4 and can hit 5.2 GHz single core boost. That would give Zen 5 roughly 32% more overall single thread performance over Zen 4 which is where that number really comes from. Done.

(I don't actually have any idea, just playing around with numbers).

how do I even say that without sounding schizo?

Perf-wise maybe, efficiency no since we're not jumping to FinFETs.So you are saying Zen 5 is giving us over Zen 4 what Zen gave us over Bulldozer?

Still, they should maintain or beat this ratio.

Still, they should maintain or beat this ratio.yeah the thing's a bit nuts, way above everyone's expectations really, so you gotta see SIR and workload performance with your own eyes to believe it.I mean it would explain why Mike Clark was super duper excited about it back when Ian interviewed him but as you say, that kind of claim is so out there it needs to be seen to be believed.

This sounds like the sentiment about the then-upcoming 5nm like two years ago.IPC is the only way companies will be able to extract performance on smaller nodes.

no, N5 was like the last real go zoomzoom node due to shiny hi-mo fins.This sounds like the sentiment about the then-upcoming 5nm like two years ago.

As for Genoa-->Turin nT performance progression, it's almost straightforward:[xyz] suggest the nT uplift isn’t 40%+.

Agreed. Should hopefully finally dispel the belief that x86 cannot scale as wide / have the same IPC as flagship premier ARM cores.I suppose this is confirmation of Z5 being the highest IPC core in the world.

Pretty clear that they have made a major breakthrough on the front end, conveniently that is the one area of the core all leaks have said nothing about.

Only shame is about the SMT yield. The fact the thing clocks comfortably over 5GHz is what will make the ARM boys head scratch.

Both it and LNC yeah.Should hopefully finally dispel the belief that x86 cannot scale as wide /

Bit like X4 core from ARM being 10 vs A17 Pro being 9 wide and still the A17P is much better.Both it and LNC yeah.

To markedly different results though.

Apple is better because it clocks higher.Bit like X4 core from ARM being 10 vs A17 Pro being 9 wide and still the A17P is much better.

If we compare X4 with A15 which has lower clock, the A15 is still better in IPC. Its just not clock.Apple is better because it clocks higher.

It's better IPC than A17p too, FYI.A15 is still better in IPC

It would be better if Strix Point (not Halo) has Infinity cache...

NoIt's better IPC than A17p too,

Bodes well for RDNA3.5 clocks then.