- Mar 3, 2017

- 1,779

- 6,798

- 136

Matheus de Souza? Hes undervolting his i9 to get those purported results.There s nothing exceptional, the guy is just unaware that his chip still consume much more than Zen 4 in this very bench which is a best case for Intel.

FI he boast 36k3 at 170W, just imagine that it s about the score of a stock 7950X3D that use barely 130W to do so, with some UV and tweaking like this one you can get at 110W.

FTR a 14900KS does 41k at stock and using 330W, so his score at 270W is not even much better overall than a stock chip.

Guess that s telling at wich point some people are in denial, seeing as great what is actually very mediocre, but hey, that s my prefered brand.

As far as I know, you can fudge the consumption numbers on Intel by tweaking AC/DC loadline settings, and considering this is WCCFtech, I'd expect this user to do so.

Do you mean 4x256b loads? I guess it's better to do 2x512 as you have to decode less instructions [or keep less of them in the uop cache] and calculate less addresses and x86 still has only 16GPRs, so it's easy to spill from GPRs to cache for some algos. It's also nice when you can fetch whole cacheline in one go. But I am probably a bit biased as 512b units are one of the zen5 selling points for meconsidering that they've improved load/store, they could have went for 4x256 which arguably is more useful than 2x512 bit, no? AVX512 in all of its forms is very niche so i was expecting improvements that were more applicable in general if the 40% ipc rumours are to be believed

Well, since low AC / DC loadline value is one of the main reasons of RPL debacle, any RPL result lowering those values, is invalid from the beginning, direct to trash.nothing like testing a new chip few days before release with undisclosed "daily PBO + CO" settings and a freaking car radiator to cool it to get headlines

Did you make an account here just to post ignorant things like this? Please get back to WCCFTECH and X and let the adults discuss. Else, please post your 45K R23 and locked 5GHz runs getting 43.3 R23, then we can talk.nothing like testing a new chip few days before release with undisclosed "daily PBO + CO" settings and a freaking car radiator to cool it to get headlines

Not bad, but ARL will likely catch up. Also, LOL at Qualcomm's chips scoring higher. Really, this isn't that impressive.While we are on the Cinebench register a slide from AMD state that Strix Point has 20% better ST perf in CB 2024 than Intel s 185H MTL.

Given that SC frequency is the same for the two chips this would imply about 20% better IPC in CB 2024 for Zen 5, and quite more uplift than the 17% IPC improvement stated for CB R23 nT.

Perhaps that our resident leaker could do a CB 2024 run to check the things, but anyway if true, and because CB relevance is galacticaly overestimated by the usual crowd, this could be quite the panic in some HQs.

Ryzen 9000/AI 300: Details zu Zen 5, RDNA 3.5, Zen 6(c) & Zen 7

Ryzen 9000 kommt am 31. Juli. Schon heute gibt es weitere technische Details zu den Desktop-CPUs und Ryzen AI 300 Strix Point für Notebooks.www.computerbase.de

If Zen 5 was server, well specifically HPC, first, I would imagine it would also feature larger, core private caches, and not SMT. And even in a general server setting, I would imagine it would focus on increasing power at the lower end of the power curve, as well as not expanding core area that much (in order to increase core density).You can get fine wine already with cachyOS with their latest Zen4/5 optimised release.

Excluding the AVX-512 datasets it’s about a 14.5% gain in IPC. It’s clear that Zen 5 is a server first architecture more than every other Zen.

Care to explain why not SMT? Mike Clark specifically said it does not have any significant area cost, and many HPC workloads absolutely benefit from it.Not bad, but ARL will likely catch up. Also, LOL at Qualcomm's chips scoring higher. Really, this isn't that impressive.

If Zen 5 was server, well specifically HPC, first, I would imagine it would also feature larger, core private caches, and not SMT.

Isn't that what the C cores are made for?And even in a general server setting, I would imagine it would focus on increasing power at the lower end of the power curve, as well as not expanding core area that much (in order to increase core density).

I would say AMD and Intel have long way to go. 5.1GHz on Strix and yet still cannot match M3 in ST performance is not a pretty sight.Not bad, but ARL will likely catch up. Also, LOL at Qualcomm's chips scoring higher. Really, this isn't that impressive.

let’s hope the person behaves here. The mods are strict and trolling is a no go.Note: This person is a known troll and Intel shill that posts regularly on WCCFTECH and X. He will bring nothing serious to the discussion here.

Here's a car radiator for you, just $100 here (you can also buy bykski 1080 battery for roughly the same, but it'd be worse in terms of fin areanothing like testing a new chip few days before release with undisclosed "daily PBO + CO" settings and a freaking car radiator to cool it to get headlines

Yes, that's precisely what I'd preferIf one could dream, these 2ADD 2FMA 512b units could turn into 4ADD 4FMA 256b units if they encountered 256b instructions

He also took one of my screenshots to claim that Zen5 is worse than Zen4 when it turned out to be slower in Blender at low PPTsNote: This person is a known troll and Intel shill that posts regularly on WCCFTECH and X. He will bring nothing serious to the discussion here.

Many HPC workloads don't benefit from SMT. Stuff like memory bandwidth limitations of workloads simply not scaling mean that SMT can worsen performance in many instances due to increased competition for resources.Care to explain why not SMT? Mike Clark specifically said it does not have any significant area cost, and many HPC workloads absolutely benefit from it.

Just because you have dense cores doesn't mean you don't want to aim for better core density with your normal products/cores as well.Isn't that what the C cores are made for?

OngI would say AMD and Intel have long way to go. 5.1GHz on Strix and yet still cannot match M3 in ST performance is not a pretty sight.

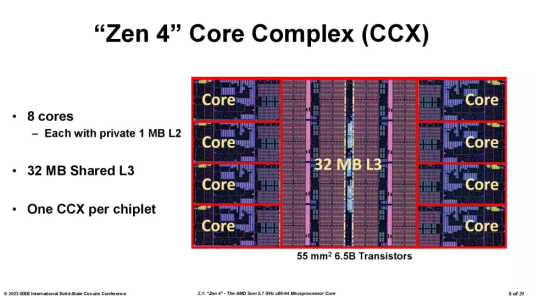

IIRC Eldora transistor density is something like 25% higher than DurangoOfficial dies sizes for the CCD of Granite Ridge (Eldora) and Strix Point:The CCD with 8x Zen 5 is 70,6 mm² – the same as Durango (CCD with Zen 4). Strix Point is growing to 232,5 mm². Both being manufactured in N4P.

You are new here so please take the time to read the CPU forum rules. Flame bait gets extinguished fast around here. You can't go in a vendor thread and start trashing and bashing that vendor or trolling the members. If you fail to comply with the rules and guidelines your stay here will be a short one.nothing like testing a new chip few days before release with undisclosed "daily PBO + CO" settings and a freaking car radiator to cool it to get headlines

If you’re not happy about how headlines are being generated, maybe you should tell your boy Hassan to stop writing articles where he’s not fully reporting all the details of the source.nothing like testing a new chip few days before release with undisclosed "daily PBO + CO" settings and a freaking car radiator to cool it to get headlines

Many HPC workloads don't benefit from SMT. Stuff like memory bandwidth limitations of workloads simply not scaling mean that SMT can worsen performance in many instances due to increased competition for resources.

Official dies sizes for the CCD of Granite Ridge (Eldora) and Strix Point:The CCD with 8x Zen 5 is 70,6 mm² – the same as Durango (CCD with Zen 4). Strix Point is growing to 232,5 mm². Both being manufactured in N4P.

Edit: according to another xitter user (do we have an official source?), zen 5 CCD has 8.315B transistors, so, ~117 MTr/mm².

Nice sleeper accountYou can't quote another member without adding your own comments.

Mod DAPUNISHER

If you’re not happy about how headlines are being generated, maybe you should tell your boy Hassan to stop writing articles where he’s not fully reporting all the details of the source.

Dude, why no analysis/comments from you about leaks/AMD Tech Day etc.? Maybe I'm not aware but I don't think you are forbidden from sharing your thoughts about Zen 5.Meds

I'm waiting until the retail stuff drops.Dude, why no analysis/comments from you about leaks/AMD Tech Day etc.? Maybe I'm not aware but I don't think you are forbidden from sharing your thoughts about Zen 5.

We have finally turned him folks. Next!I'm waiting until the retail stuff drops.

Meds