- Mar 3, 2017

- 1,774

- 6,757

- 136

Amazing, were did you find that?Yikes, looks like the rumor of Zen 5 + Zen 4D could be true after all

View attachment 78615

View attachment 78612

Reading Family ID is not sufficient anymore, now there are core level differences and the CPU Topology has to be read as well.

Same thought, I only want the Zen 5 cores, not some puny outdated Zen 4cinebenchcores.

I would guess one 8C Zen 5 Chiplet + 16C Zen 4 Chiplet for 24C.

So going by PHX2 topology, Zen 4c would have half the L3 per Core but for 16C in one CCX the amount of L3 would still be same? That could make L3 available to a core to the SW pretty much same even though L3 per core is half. But overall around same size as Zen 4 CCD but 2x cores, if going with PHX density of 25 MTr@178mm2

View attachment 78613

Meh. Give me 24 Zen5 cores not these hybrids. If i wanted that, i could get Intel CPU.

BTW, only now read about Turin etc...was not paying attention to these future Epycs and whatnot before, last thing i knew was Zen4 Genoa 96C and Zen4C Bergamo 128C. So is Turin Zen5 = Genoa replacement and supposedly up to 192 cores, did i understand that right? And if yes, they are still keeping 8 cores per chiplet? Cause that would be 24 chiplets on one CPU...is it going to have 24 RAM channels? Or would 2 chiplets share single channel? Somehow i find this hard to believe to be truth...then again, what do i know.

I think Turin will have 16 x 8 Core CCDs = 128

The Bergamo successor will likely have 12 x 16 core CCDs = 192

The socket stays the same, so the same 12 channels of memory.

Zen 4C CCD is 50% bigger than the Zen 4 chiplet?Same thought, I only want the Zen 5 cores, not some puny outdated Zen 4cinebenchcores.

I would guess one 8C Zen 5 Chiplet + 16C Zen 4 Chiplet for 24C.

So going by PHX2 topology, Zen 4c would have half the L3 per Core but for 16C in one CCX the amount of L3 would still be same? That could make L3 available to a core to the SW pretty much same even though L3 per core is half. But overall around same size as Zen 4 CCD but 2x cores, if going with PHX density of 25 MTr@178mm2

View attachment 78613

From the manual for Phoenix and the generic architecture reference document.Amazing, were did you find that?

Slowly but surely all my wild speculations come true.

Next stop: IFoP successor 😎

N4P should be enough for Zen 4 to reach 6.2 GHz. N4X is leaky and density is not great, from commercial perspective it will be not suitable for Zen 4.The only thing I can see happening is AMD moving Zen 4 to a custom N4X for a November release. Zen 4 is smaller and the improved process can probably hit 6.2 Ghz. This extra clock speed would allow AMD to better compete with Intel in the mid to low-end retail space while Zen 5 takes the high end.

PHX has a density of 140MTr/mm2. And the Zen 4 cores there hit 5.2 GHz. 16C Zen 4c with half L3 fabbed like this will be similar to a standard 8C Zen 4 chiplet in size, ~66 mm2.Zen 4C CCD is 50% bigger than the Zen 4 chiplet?

If Zen 5 uses that, I don't expect prices to be pretty for consumers

That can't be the case.Especially since I think, at best, the Zen 5 chiplet is going to be the same size as the Zen 4 standard chiplet.

Actually good point why Zen 4c, why not Zen 5c. But AMD differentiate efficiency cores from performance cores based on process efficiency mainly so they might not be ready to fab Zen 5c on N3E yet.Also, why use a Zen 4C chiplet anyway? Do we even know if Zen 4C will offer better MT perf/mm^2 or perf/cost than Zen 5? Over Zen 4 it's obvious, but for Zen 5 idk, since the node is similar so costs would be similar there, and Zen 5 should offer significant IPC gains... maybe if someone can do some rough napkin math for how much better Zen 5 would have to be to get better perf/watt over Zen4C...

If they do end up using Zen 4C though, hopefully we get a Zen 5 with V-cache and Zen 4C chiplet as an option...

Meh. Give me 24 Zen5 cores not these hybrids. If i wanted that, i could get Intel CPU.

BTW, only now read about Turin etc...was not paying attention to these future Epycs and whatnot before, last thing i knew was Zen4 Genoa 96C and Zen4C Bergamo 128C. So is Turin Zen5 = Genoa replacement and supposedly up to 192 cores, did i understand that right? And if yes, they are still keeping 8 cores per chiplet? Cause that would be 24 chiplets on one CPU...is it going to have 24 RAM channels? Or would 2 chiplets share single channel? Somehow i find this hard to believe to be truth...then again, what do i know.

When comes to dual CCD designs like Raphael it's close to impossible since the IO is limited to 8 core per CCD,

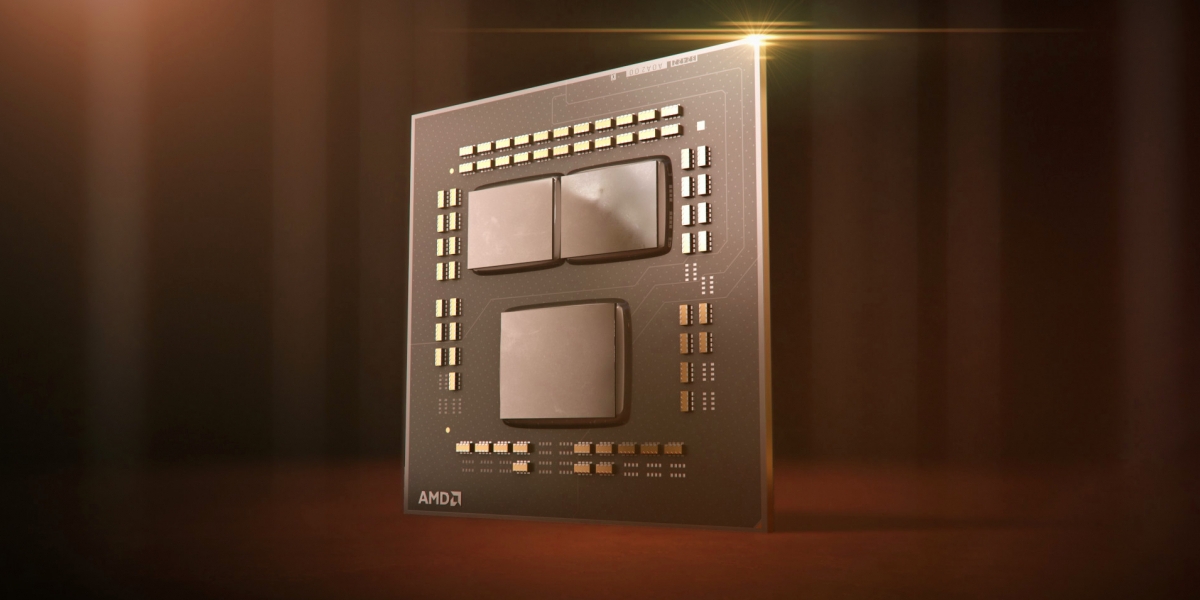

The CCDs in MI300 are on top of the base I/O die and connected via SoIC.It is about certain that one Zen4c Bergamo CCD is housing 2 CCX with 8 cores each. These two CCX do not share their L3, just as was the case with Zen2.

Regarding the interconnect to the IOD the picture is much more blurry:

- One option is: The current EPYC IOD has 12 IFoP links. So the up to 8 Bergamo CCD could get connected via one link each. That could get them bandwidth starved as this is only half the bandwidth per core as Desktop and Server Zen4 have.

- Another option: From my measurements it seems, that MI300 employs 24 Zen4c cores, not Zen4. One die could be the plain old 16c die for Bergamo. And that might be connected via Infinity Fan-out Links AKA InFO-RDL. This would bring them plenty bandwidth even with a rather narrow link. So for me it is quite possible, that starting with Bergamo and later on with Desktop Zen5 AMD will get rid of the current IFoP.

Right, they are connected to a base die via SoIC. But how are the four base dies connected to HBM and quite likely each other as well? The most likely answer after having a look at N31 is InFO-RDL. Another option would be EFB for connecting the base dies to each other.The CCDs in MI300 are on top of the base I/O die and connected via SoIC.

Not InFO-RDL very likely , the BW requirements for the GPU SEs is massive. LSI and/or EFB.But how are the four base dies connected to HBM and quite likely each other as well?

Well, for the MCD in N31 we already have 1 TByte/s. This can be increased quite easily by using more beachfront.Not InFO-RDL very likely , the BW requirements for the GPU SEs is massive. LSI and/or EFB.

www.kitguru.net

www.kitguru.net

www.sportskeeda.com

www.sportskeeda.com

Well, for the MCD in N31 we already have 1 TByte/s. This can be increased quite easily by using more beachfront.

Apple's M1 Ultra, which employs InFO-LSI or EFB also has only 2.5 Tbyte/s.

So you are saying, they may have decreased TSMC's pj/bit figures by lowering the GByte/mm as well through lower clocks?Apple is using a massive number of I/Os clocked fairly slowly to minimize power consumption. It is the result of a different set of goals.

So you are saying, they may have decreased TSMC's pj/bit figures by lowering the GByte/mm as well through lower clocks?

as i suspected it's another xt. sit back and wait for @DrMrLordX to complain about the xts again.Zen 5 is definitely not coming in 2023. AMD stated that it is a 2024 product. And since AMD refreshes their mobile line up every March, and has stated that the next mobile chip is based on Zen 5, we can conclude that Zen 5 should be out in March or April 2024.

The only thing I can see happening is AMD moving Zen 4 to a custom N4X for a November release. Zen 4 is smaller and the improved process can probably hit 6.2 Ghz. This extra clock speed would allow AMD to better compete with Intel in the mid to low-end retail space while Zen 5 takes the high end.

as i suspected it's another xt. sit back and wait for @DrMrLordX to complain about the xts again.

I can just remark that thanks to Intel flooding the CPUs with E cores it is very hard to compete with them in the low/mid end market segment.This extra clock speed would allow AMD to better compete with Intel in the mid to low-end retail space while Zen 5 takes the high end.

Nothing, he doesn't want to admit he's fussy about AMD's release schedule. the pandemic messed up their scheduling. IIRC Zen 4 was later than expected at 24 months. Zen 5 returns to the 14-18 month schedule they had prior.I dont understand what should I complain about...

| Name | Model | Launch Date | Node | CPU cores | L3 Cache | Memory LPDDR5x | Memory BW | GPU | ALU | IC | TDP |

|---|---|---|---|---|---|---|---|---|---|---|---|

| PHX2 | R5 7040 | Q3 2023 | N4 115mm2 | 2xZen4 + 4xZen4c | 4+4=8MB | 64-bit 7500 | 60 GB/s | RDNA3 4CU 256SP | 256 | NA | 15W |

| STX3 | R5 8050 | Q3 2024 | N4P | 2xZen5 + 4xZen5c | 12 MB | 64-bit 8533 | 68 GB/s | RDNA3+ 4CU 256SP | 512 | NA | 15W |

| PHX+ | R7&9 8040 | Q1 2024 | N4P | 8xZen4 | 16 MB | 128-bit 8533 | 136 GB/s | RDNA3+ 12CU 768SP | 1536 | NA | 15-45W |

| STX2 | R7 8050 | Q3 2024 | N4P | 4xZen5 + 8xZen5c | 24 MB | 128-bit 8533 | 136 GB/s | RDNA3+ 8CU 512SP | 1024 | NA | 15-45W |

| STX1 Halo | R9 8050 | Q3 2024 | N4P + N4P | 8xZen5 + 8xZen5c | 32 MB | 256-bit 8533 | 272 GB/s | RDNA3+ 20CU 1280SP | 2560 | 32MB | 25-120W |

| 6xZen5 + 8xZen5c | 28 MB | 128-bit 8533 | 136 GB/s | RDNA3+ 10CU 640SP | 1280 | 32MB | |||||

| Fire Range | R7&9 8055 | Q3 2024 | N4P x 3 | 16xZen5 | 64 MB | 128-bit | RDNA3+ 2CU 128SP | 256 | NA | 55W+ |

There is new leaks from RGT about Strix Point, AMD seems like going to split the APU design into 3 die, below is comparison table:

PHX2 N4 115mm2 2xZen4 + 4xZen4c 8MB RDNA3 4CU 256SP 15W STX3 N4P 2xZen5 + 4xZen4c 8MB RDNA3+ 4CU 256SP 15W STX2 N4P 4xZen5 + 8xZen4c 16MB RDNA3+ 8CU 512SP ~30W? STX1 N3E 8xZen5 + 8xZen4c 32MB RDNA3+ 16CU 1024SP ~35W?

Guess AMD still going monolithic with Strix Point with 3 different dies