poke01

Diamond Member

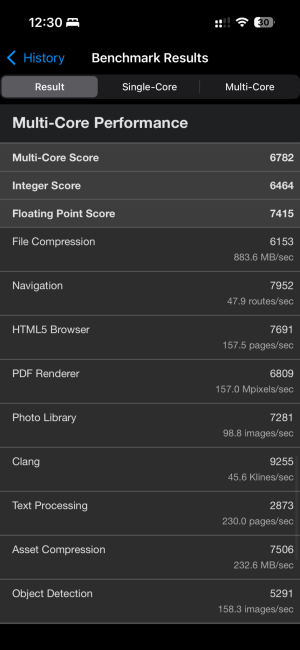

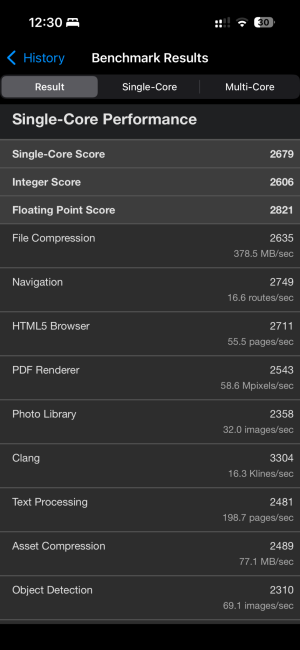

Do you think SME was created for cheating in Geekbench?never implied that I only meant that cheating in GB with cluster level hacks is something I dislike.

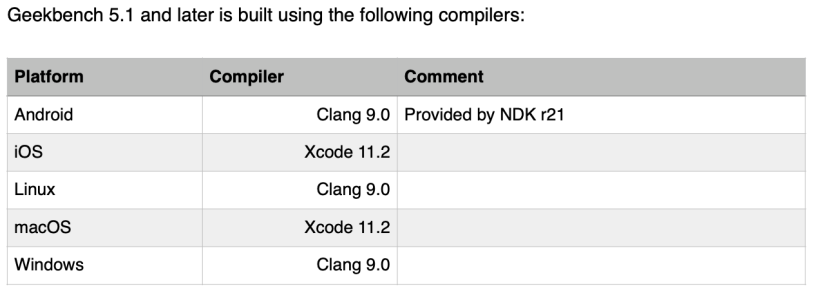

Apple has had matrix mul accelerators since the A13. But it was never exposed to devs until SME was standardised by ARM.