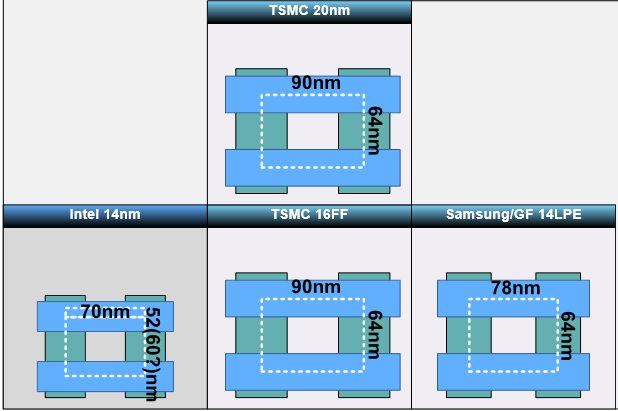

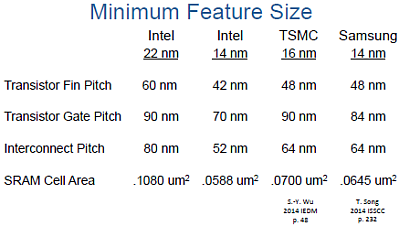

1) Could someone make clear this question please? I know that different chip-makers differently name their manufacturing process, and it is rather a marketing term. Wikipedia says that the naming of this technology node as "14 nm" came from the International Technology Roadmap for Semiconductors (ITRS). So does it mean "14 nm" is an abstract term, which dose not refer to any transistor's component? Then why 14 nm and not 16 nm?

2) As far as I know quantum effects will arise when transistor gate pitch becomes less than 5-1 nm. According to Intel transistor gate pitch in it's 14 nm Process Technology is 70 nm. Does it mean that 5-1 nm is far, far away, and it's not correct to make forecasts based on today's marketing "14 nm"?

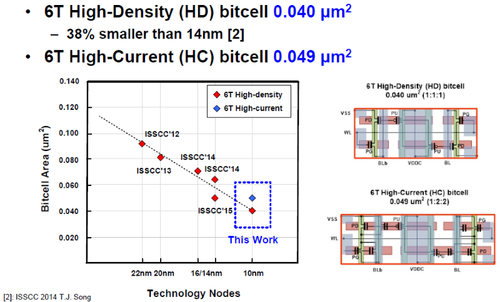

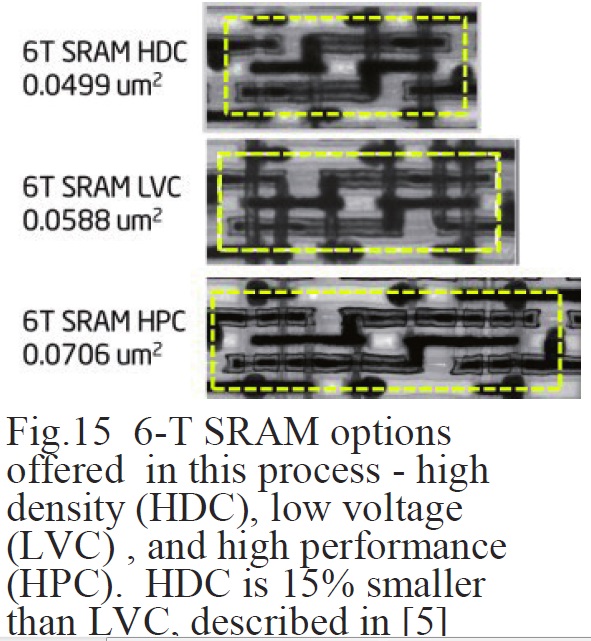

3) Won't it be more correct to compare actual number of transistors per square mm - instead of all these nanometers? Or transistors on different chips are also of different size?

2) As far as I know quantum effects will arise when transistor gate pitch becomes less than 5-1 nm. According to Intel transistor gate pitch in it's 14 nm Process Technology is 70 nm. Does it mean that 5-1 nm is far, far away, and it's not correct to make forecasts based on today's marketing "14 nm"?

3) Won't it be more correct to compare actual number of transistors per square mm - instead of all these nanometers? Or transistors on different chips are also of different size?