witeken

Diamond Member

Dropping the frequency target by over 1 GHz? I have to imagine they will have re-run their physical design flows. I mean, you work at Intel so I differ to you but I can't believe that's how it goes. If so, well I guess I know one reason Core M didn't deliver as expected compared to ARM designs which are always implemented for particular targets. I mean you have an extra 170ps going between 3 and 2 GHz, does process variation eat all of that up in binning? Maybe it does, I guess I don't know 14nm parameters. I am completely aware of the cost in man-hours, but the cost of releasing sub-par products seems awful high - well something to the tune of $4.21 billion I think 😀

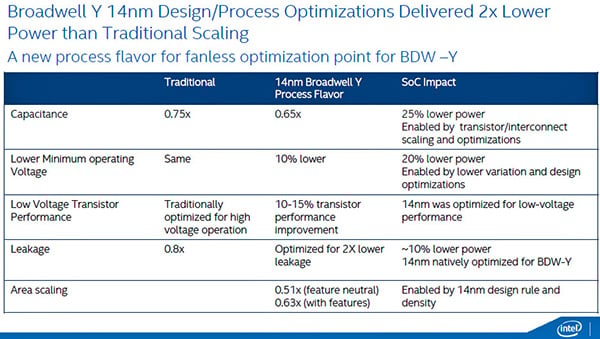

According to Intel, 14nm was natively optimized for BDW-Y.