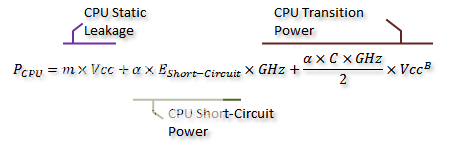

Since my asus maximus iv extreme-z has this nice convenient bank of voltage monitoring points (ASUS calls it "ProbeIt"), I thought I would have some geeky "sciency" fun armed with my i7-2600K, a volt-meter, a kill-a-watt power meter, and a garden variety rudimentary understanding of the analytical equations that express the power-consumption of my CPU as a function of clockspeed and operating voltage

Here's the ProbeIt voltage monitoring bank:

Kill-A-Watt setup (alongside a 30-100dB range sound meter and an ambient temperature probe):

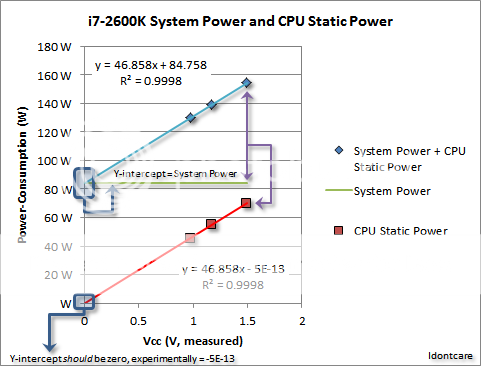

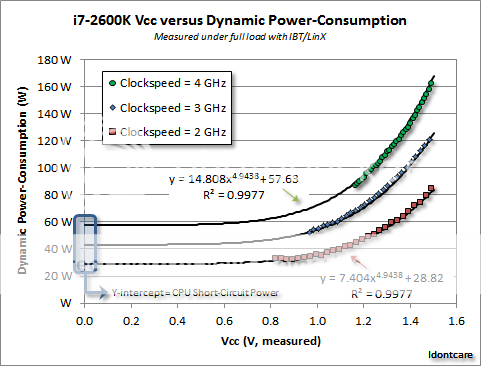

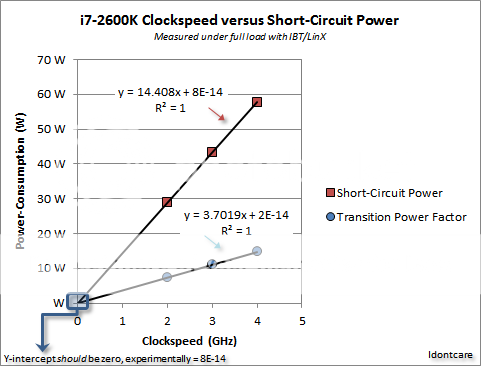

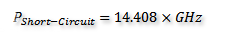

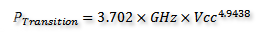

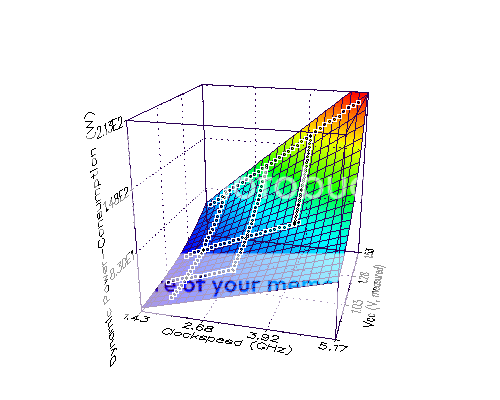

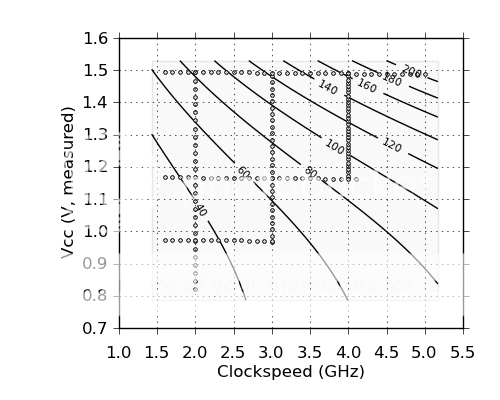

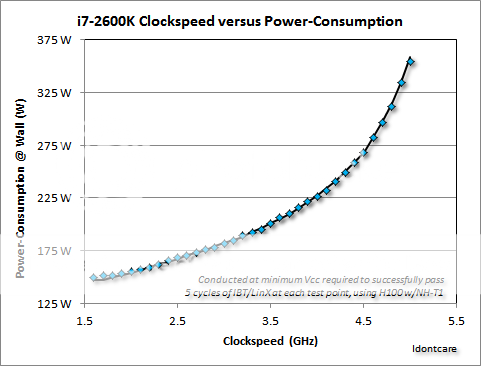

Armed with these data probes, I proceeded to test my 2600K at every multiplier value available from 16x to 50x (for these tests I did not go above 50x).

Some specs on the other hardware components - the rig is equipped with 4x4GB GSkill F3-17000CL11Q-16GBXL 1.5V rated at DDR3-2133 (but only running at DDR3-1866 10-10-10-28-T1 @ 1.5V), a delidded GTX460 905MHz/1.1V, a lapped 2600K and lapped H100 for cooling using NT-H1 TIM, powered by CORSAIR Gold AX850 (CMPSU-850AX) w/>90% efficiency.

In the first set of tests, what I did was (1) select the CPU multiplier from within using TurboV EVO, (2) run LinX w/4-threads (affinity locked to physical cores) with 14.2GB of ram set to complete 5 passes.

If the CPU completes the run successfully (no errors detected, or BSOD's or reboots) then I take the voltage down by 0.005 V (the minimum step allowed with TurboV EVO) and do another run of 5 cycles in IBT.

Once I found the minimum Vcc for which the CPU is stable enough to fully pass 5 cycles of IBT, I logged the peak temperature, peak power-consumption, ambient temperature, etc, and then incremented the multiplier and repeated the process all over again.

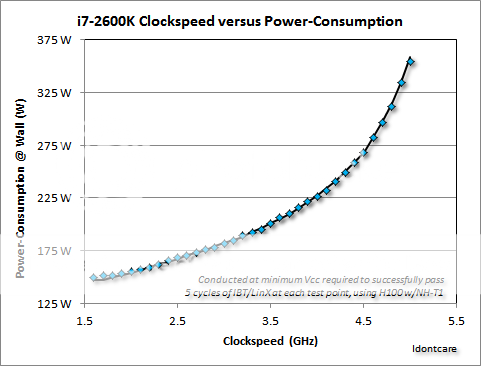

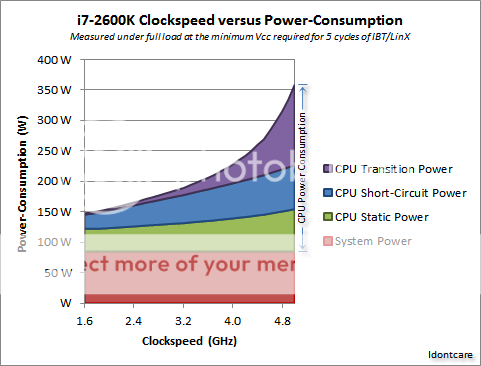

The result of this somewhat laborious process was the following graph of clockspeed versus power-consumption:

Here's the ProbeIt voltage monitoring bank:

Kill-A-Watt setup (alongside a 30-100dB range sound meter and an ambient temperature probe):

Armed with these data probes, I proceeded to test my 2600K at every multiplier value available from 16x to 50x (for these tests I did not go above 50x).

Some specs on the other hardware components - the rig is equipped with 4x4GB GSkill F3-17000CL11Q-16GBXL 1.5V rated at DDR3-2133 (but only running at DDR3-1866 10-10-10-28-T1 @ 1.5V), a delidded GTX460 905MHz/1.1V, a lapped 2600K and lapped H100 for cooling using NT-H1 TIM, powered by CORSAIR Gold AX850 (CMPSU-850AX) w/>90% efficiency.

In the first set of tests, what I did was (1) select the CPU multiplier from within using TurboV EVO, (2) run LinX w/4-threads (affinity locked to physical cores) with 14.2GB of ram set to complete 5 passes.

If the CPU completes the run successfully (no errors detected, or BSOD's or reboots) then I take the voltage down by 0.005 V (the minimum step allowed with TurboV EVO) and do another run of 5 cycles in IBT.

Once I found the minimum Vcc for which the CPU is stable enough to fully pass 5 cycles of IBT, I logged the peak temperature, peak power-consumption, ambient temperature, etc, and then incremented the multiplier and repeated the process all over again.

The result of this somewhat laborious process was the following graph of clockspeed versus power-consumption: