IDK about SKU but the plan to make 4+8 using 18AP is canned it is using TSMC N2 now

Are you 100% confident about this? Because they already have a 4P+8E die on 18A for PTL-H? so it shouldn't be a big deal do that in 18A-P to do the same considering its just a related + node. At least what is what I thought. Also NVL is already taped out by the time Foundry direct connect 2025 event & shortly afterwards semiaccurate reported NVL SKUs on N2 taped out, I highly doubt Lip Bu Tan could have changed something on NVL by then.

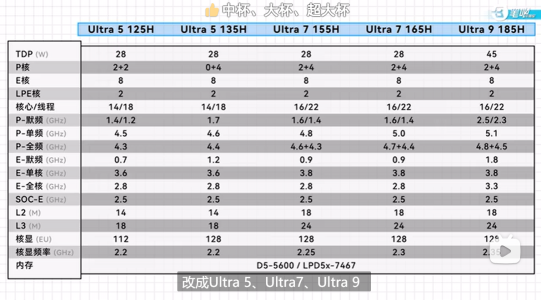

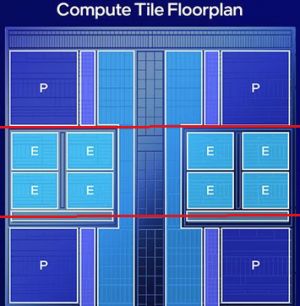

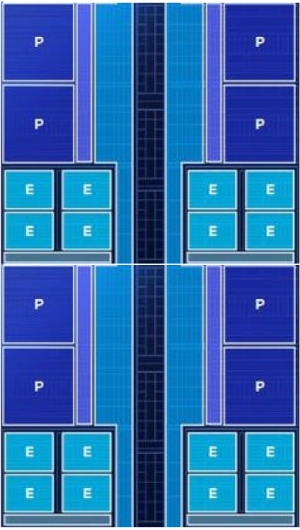

Just from engineering POV to reduce engineering effort, to leverage tile arch & benefit from it, it makes sense to do one 8P+16E die on N2P & one 4P+8E die on 18A/18A-P. Then they can mix and match to create SKUs & down bin the 4+8 die to 4+4 & 4+0.

Note if 4+8 die is on 18A/18A-P, the entire mobile line up on NVL- H will be IFS (like PTL-H but on 18A-P), only the NVL-HX (8+16) will be on TSMC. I think this is very important for Intel to regain their margins. So it just baffles me that 4+8 would be on TSMC & that decision being made Lip Bu doesn't sound right with me. He is looking to be bean counter when it comes margins based on recent news about new product being approved only if margin >50%. Intel can't afford to keep outsourcing their products and maintain upkeep of their foundries which are fixed cost business.

This aligns with past commentaries from Pat & Michelle also that NVL is predominantly IFS based (Pat quoted >80% iirc) and only one top end SKU is on TSMC node. Also why MLID is keeping the 4+8 SKU as "high confidence" color instead of "very high confident" color. He is intentionally downplaying 18A-P imho.

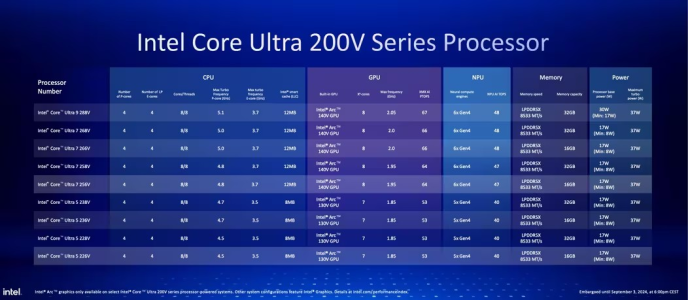

I think Intel is only sourcing the 8P+16E bLLC die from TSMC. With that they can make a 2(8P+16E bLLC)+4LPE SKU for a Core Ultra 9, (8P+16E bLLC & 4P+8E[18A-P])+4LPE SKU for Core Ultra 7 & (8P+16E bLLC)+ 4LE for Core Ultra 5 that covers all the gaming crowd requirements of a bLLC SKU to compete with x3D. All these will be K SKUs. All the rest of the main stream K & non K SKUs will be based on 18A-P tiles like 2(4+8)+4LPE, 4+8+4LPE, 4+0+4LPE. This way they limit the outsourcing to TSMC to the minimum. This is just speculation on my part but who knows what is really going on at Intel now!