It has Y cruncher in the mix with AVX-512 when NVL will get AVX-512 there would be a change in it if in handbrake they are using SVT-AV1 it also supports AVX-512 .

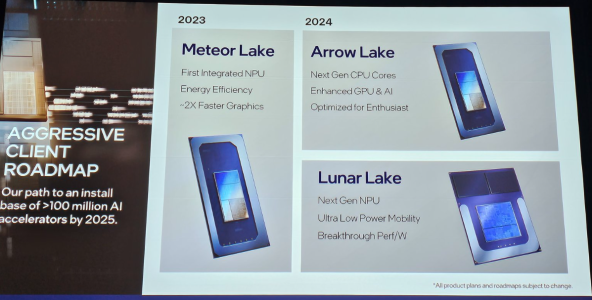

It is my understanding that only the DC versions of Intel processors will be getting AVX-512.... and that isn't even true since I believe Intel is pushing AVX10 to unify their 512 and 256 bit instruction vectors across P and E cores. Still, you are correct that should Nova Lake include AVX10, and should people recompile to support this instruction set, things would look better for Intel in some of these benchmarks; however, I still believe Zen 6 will dominate due to full width AVX512 support across all cores at full speed. Additionally, Tom's benchmarks also included CB24 which is currently quite bandwidth limited. Zen 6 is likely to make inroads on CB24 which Zen 5 currently gets beaten badly by Arrow Lake in. This will balance things out a little I think.

I am guessing that Zen 6 still dominates MT on a per core basis since it includes SMT on every core. I wouldn't be surprised if a single Zen 6 core is equal to 1.5 Nova Lake cores. We will see I guess.

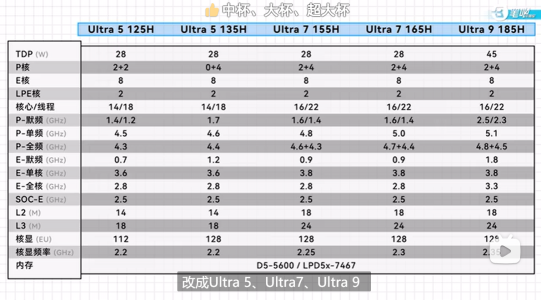

THe SKU can be but not limited to

- 8+16+4

- 2*(8+16)+4

- 2*(4+8)+4

- 4+8+4

- 4+0+4

the 8+16 Tile is N2 and the 4+8+4/4+0 tile is 18AP and the common SoC tile is shared across all the SKUs.

So we have Nova Lake variants of:

- 28c

- 52c

- 28c (different flavor)

- 8c

... against a lineup of Zen 6 having at least:

Also, I wonder about the 4 LP cores. Seems like these will do much more for marketing than they do for benchmarks. So for benchmark purposes perhaps it is more accurate to say Nova Lake looks like:

- 24c

- 48c

- 24c (different flavor)

- 4c

Still, at 1.5:1, the 24c Zen 6 will still only be able to do MT of 36 Nova Lake cores giving the big Nova Lake part a commanding lead in MT ..... assuming it does not become bandwidth starved.

In automotive, I have always mused that an internal combustion engine is really just an air pump. The more air you can get it to move, the more power it creates.

Processors aren't that different IMO. You have to move memory in and out to do work. The more cylinders you have (cores) the wider the air intake and exhaust needs to be to feed it (memory bandwidth).