I think their chances are great if they put a low latency (<50 ns) 128MB cache in the SoC tile for 16P Nova Lake. For gaming workloads, the CPU shouldn't consume more than 125W overall. If they can manage at least 15% IPC increase over Lion Cove with guaranteed 5.5 GHz clocks, they may manage to be competitive with Zen 6.

Even if so, it will still be behind current X3D and most certainly behind Zen 6 X3D. I think Intel needs an answer to X3D technology that drastically lowers memory latency. The current ARL design already has huge issues in latency. I think they will be doing good just to free up the current design, rather on starting with expectations of Zen 5 and expecting latency improvements so drastic in Nova Lake that it surpasses X3D.

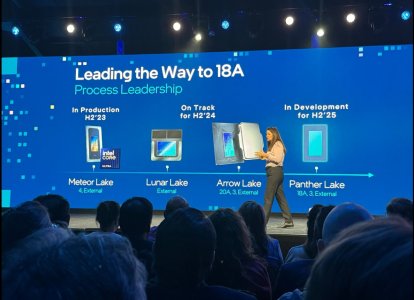

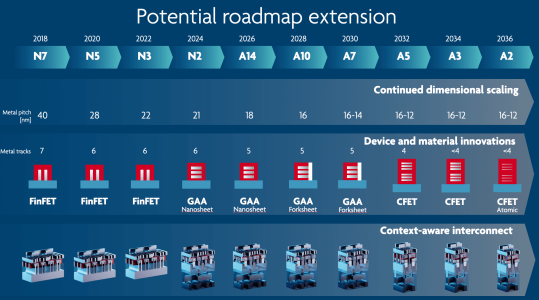

Keep in mind, moving from N3B to 18A is not going to give Intel much additional transistor budget to work with (unlike the move to N3B did).

The IPC Estimate should be 20% or more considering we are getting both a Tick (Cougar) and Tock(Panther Cove) and fixing lost IPC From ARL

... and this is how people got so disappointed by ARL. You take all the little leaks, add up the IPC improvements you see in each change, then sum them all up to get a really big number ..... and then are very disappointed when the product comes out as all these theoretical improvements don't translate into real world performance.

As I stated above, the additional transistor budget expected by 18A over N3B shouldn't be expected to gain much IPC as cache, logic buffers, TLA, front end, execution units, etc, etc, wont likely be afforded much growth.

I expect some good improvements in some applications if Intel can just get their latency under control. Others (that are already doing well on ARL) wont gain much at all.

I think the days of 20% IPC increases are over inluess it is being compared to a previous architecture that is broken in some way..

I agree, because the days of getting 50% higher transistor budget are ALSO over

.